Table des matières:

- Étape 1: Configurer la logique programmable Zynq pour l'émetteur

- Étape 2: Configurer la logique programmable Zynq pour le récepteur

- Étape 3: configuration du pilote VDMA

- Étape 4: Configurer le réseau de nanorouteurs

- Étape 5: Configurer le système de traitement Zynq pour la transmission de données via Ethernet

- Étape 6: Configurer le système de traitement Zynq pour la réception de données via Ethernet

- Étape 7: connectez vos cartes Zybo à la source HDMI et à l'évier HDMI

- Étape 8: Idées alternatives d'amélioration

- Étape 9: Accessibilité

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:08.

- Dernière modifié 2025-01-23 14:46.

Avez-vous déjà souhaité pouvoir connecter votre téléviseur à un PC ou à un ordinateur portable en tant que moniteur externe, mais vous ne vouliez pas avoir tous ces cordons embêtants? Si c'est le cas, ce tutoriel est fait pour vous ! Bien que certains produits atteignent cet objectif, un projet de bricolage est beaucoup plus satisfaisant et potentiellement moins cher.

Ce concept est différent des produits comme Chromecast, car il est destiné à remplacer un cordon HDMI connecté à un moniteur au lieu d'être un appareil de streaming.

Notre projet a été créé en tant que projet final pour un cours sur les systèmes d'exploitation en temps réel à la California State Polytechnic University, San Luis Obispo.

L'objectif du projet est d'utiliser deux cartes Digilent Zybo pour servir d'interface de communication sans fil entre un périphérique émetteur HDMI (PC, Blu-ray, etc.) et un périphérique de réception HDMI (moniteur de bureau, projecteur, téléviseur, etc.).

Un Digilent Zybo sera connecté via HDMI à l'appareil de transmission, et l'autre sera connecté via HDMI à l'appareil de réception.

La communication sans fil sera effectuée en utilisant un réseau local sans fil dédié à l'émetteur et au récepteur, sans être acheminée via un routeur domestique ou un autre appareil de ce type. Le module sans fil utilisé pour ce projet est le nanorouteur tplink wr802n, dont l'un fonctionne comme un point d'accès pour établir le réseau et l'autre pour fonctionner comme un client pour se connecter au réseau. Chaque nanorouteur sera connecté via un câble Ethernet à l'une ou l'autre des cartes Zybo. Lorsqu'ils sont connectés à ces routeurs, les appareils communiquent via TCP comme s'ils étaient connectés avec un seul câble Ethernet (ce qui signifie que la seule configuration nécessaire pour établir une connexion est l'adresse IP du client).

Alors que l'objectif du projet était de faciliter un flux vidéo 1080x720 à 60 Hz, cela n'a pas été réalisable en raison des limitations de bande passante du réseau sans fil et du manque de compression vidéo en temps réel pour réduire les données nécessaires à l'envoi. Au lieu de cela, ce projet sert de cadre pour le développement futur pour atteindre cet objectif, car il a des limitations sévères de la fréquence d'images pour diffuser correctement les données HDMI comme prévu.

Exigences du projet:

2x cartes de développement Digilent Zybo (doit avoir au moins un port HDMI)

2x câbles HDMI

2x câbles microusb (pour connecter Zybo au PC pour le développement)

2x nanorouteurs tplink wr802n (y compris 2x adaptateurs microusb et prise murale)

2x câbles Ethernet

***Remarque: Ce didacticiel suppose une familiarité avec la suite de conception Vivado et une expérience de la création d'un nouveau projet et de la conception de blocs.***

Étape 1: Configurer la logique programmable Zynq pour l'émetteur

Notre approche pour développer la logique programmable de l'émetteur consistait à effectuer une transmission HDMI à HDMI du PC au moniteur à l'aide de deux blocs d'accès direct à la mémoire vidéo (VDMA), un pour l'écriture et un pour la lecture.

Les deux sont sélectionnés pour un mode de mémoire tampon à 3 images à exécution libre (0-1-2). Étant donné que le noyau vidéo est optimisé pour 60 images par seconde, cela signifie que le VDMA écrira ou lira une nouvelle image toutes les 16,67 ms dans cet ordre: 0, 1, 2, 0, 1, 2, 0, 1, 2. Les emplacements de mémoire DDR pour chaque trame sont différents pour les deux VDMA car ils ne sont plus synchronisés entre eux. Au lieu de cela, un temporisateur matériel (TTC1), configuré pour 60 Hz, est utilisé pour synchroniser le mouvement des données entre les deux emplacements mémoire.

L'image ci-dessus montre 3 cadres, leurs dimensions et la quantité de mémoire que chacun nécessite (à droite du cadre). Si nous attribuons le VDMA d'écriture à ces emplacements de mémoire, nous pouvons alors affecter les emplacements de mémoire VDMA de lecture au-delà de cet ensemble, disons en commençant par 0x0B000000. Chaque image est composée de 1280*720 pixels et chaque pixel est composé de 8 bits de Rouge, Vert et Bleu pour un total de 24 bits. Cela signifie qu'une trame est composée de 1280*720*3 octets (2,76 Mo).

À l'intérieur du temporisateur, l'IRQ, qui est décrit dans la configuration du pilote VDMA, gérera la copie des données entre les deux emplacements de mémoire VMDA. Le VDMA fournit un pointeur vers la trame en cours d'écriture ou de lecture. La trame est représentée par un code gray particulier, qui est converti en logiciel. Les définitions du code gray pour une configuration de mémoire tampon à 3 images se trouvent dans le Guide produit AXI VDMA en annexe C.

Cela nous permet de copier le contenu en cours d'écriture dans la mémoire sans lire à partir d'une trame en cours d'écriture.

***Notez que le VDMA lu n'est pas utilisé lors de l'envoi de données sur le réseau sans fil. Son seul but est de vérifier le bon fonctionnement de la copie de mémoire à partir du VMDA d'écriture. La lecture VMDA doit être désactivée.***

Voici les étapes pour créer le bloc de conception du transmetteur:

- Lors de la création d'un nouveau projet, il est judicieux d'attribuer une puce ou une carte au projet. Ce lien décrit comment ajouter de nouveaux fichiers de carte au répertoire Vivado et associer la bonne carte à votre projet. Cela vous sera utile lors de l'ajout du bloc Processing System et de la transition du matériel au logiciel (côté SDK).

-

Ajoutez les blocs suivants:

- dvi2rgb

- Vidéo dans le flux Axi4

- Contrôleur de synchronisation

- axi4-stream à vid out

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Assistant d'horloge

- Constant

- Système de traitement Zynq

- Lors de l'ajout du système de traitement, cliquez sur « Exécuter l'automatisation des blocs » dans la barre de couleur verte supérieure et assurez-vous que l'option « Appliquer le préréglage de la carte » est sélectionnée. Laissez tout le reste par défaut.

- Des images de chaque fenêtre de configuration de bloc peuvent être trouvées dans les images ci-dessus. Si vous ne voyez pas d'image pour une fenêtre particulière, laissez-la par défaut.

-

Commencez à configurer le système de traitement Zynq:

- Dans la configuration PS-PL AXI non sécurisé Activer GP Master AXI, activer l'interface M AXI GP0

- Dans la configuration PS-PL HP Slave AXI Interface, activez à la fois HP0 et HP1

- Dans la configuration MIO, assurez-vous que ENET0 est activé sous Périphériques d'E/S, puis Unité de processeur d'application, activez Timer0

- Dans Clock Configuration PL Fabric Clocks, activez FCLK_CLK0 et définissez-le sur 100 MHz.

- Cliquez sur OK

- Avant de cliquer sur « Exécuter l'automatisation de la connexion », assurez-vous de connecter les blocs vidéo comme indiqué dans l'image de conception de bloc TX ci-dessus. Vous voudrez renommer la constante en VDD et définir la valeur sur 1. Connectez les blocs vidéo en conséquence.

- Rendre l'horloge HDMI TMDS et les broches de données externes sur les blocs rgb2dvi et dvi2rgb

- Créez un port d'entrée et de sortie pour le signal de détection de branchement à chaud (HPD) et connectez-les ensemble, ceux-ci sont définis dans le fichier de contraintes

-

L'horloge pixel est récupérée à partir du TMDS_Clk_p, qui est créé dans le fichier de contraintes. Ce sera 74,25 MHz conformément à la résolution 720p. Il est important de connecter l'horloge pixel (du bloc dvi2rgb) aux broches suivantes:

- vid_io_in_clk (vid dans le bloc de flux axi)

- vid_io_out_clk (flux axi vers bloc de sortie vidéo)

- clk (contrôleur de synchronisation)

- PixelClk (rgb2dvi)

- ***Remarque: Actuellement, pour activer la récupération de l'horloge des pixels, les connecteurs HDMI rx et tx doivent être branchés sur une source/un récepteur actif. Une solution consiste à séparer les blocs vidéo rx et tx en différents domaines d'horloge (en d'autres termes, générer une nouvelle horloge à 74,25 MHz pour alimenter le bloc tx).***

- Configurez ensuite l'assistant d'horloge de sorte que vous ayez une entrée de 100 MHz (source tampon globale) et 3 horloges de sortie à 50 MHz (horloge AXI-Lite), 150 MHz (horloge AXI4-Stream), 200 MHz (broche dvi2rgb RefClk).

- Connectez la broche du système de traitement FCLK_CLK0 à l'entrée de l'assistant d'horloge

- À ce stade, cliquez sur « Exécuter l'automatisation de la connexion » dans la barre verte en haut de la fenêtre de conception. C'est une bonne idée de faire cela pour un bloc à la fois et de suivre l'image de conception de bloc TX ci-dessus.

- L'outil tentera d'ajouter l'interconnexion AXI, qui agit comme l'interconnexion maître/esclave pour les blocs qui utilisent le bus AXI-Lite (VDMA et GPIO).

- Il ajoutera également AXI SmartConnect, qui agit comme l'interconnexion maître/esclave pour les interfaces de processeur AXI4-Stream et High Performance utilisées par le VDMA (Stream to Memory Map et vice versa).

- L'outil ajoutera également une réinitialisation du système de processeur. Assurez-vous qu'il n'est connecté qu'aux VDMA, GPIO et blocs liés au processeur. Ne le connectez à aucun bloc vidéo (c'est-à-dire dvi2rgb, contrôleur de synchronisation, vid to stream, etc.)

- Une fois l'automatisation des connexions terminée, vérifiez que les connexions correspondent à celles de l'image de conception du bloc TX. Vous remarquerez un bloc System ILA supplémentaire qui n'a pas été mentionné. Ceci est uniquement destiné au débogage et n'est pas nécessaire pour le moment. Il utilise la réinitialisation du processeur 150M, ce qui n'est donc pas nécessaire non plus. Partout où vous voyez de petits "bugs" verts sur les bus, c'est à cause de l'ILA et peuvent être ignorés.

- La dernière étape consiste à cliquer avec le bouton droit sur la conception du bloc dans l'arborescence des sources du projet et à sélectionner "Créer un wrapper HDL". Si vous prévoyez d'ajouter de la logique au wrapper, elle sera écrasée à chaque fois qu'elle est sélectionnée.

- Consultez la section Configuration du pilote VDMA pour plus de détails sur le SDK.

Horloges et réinitialisations

J'ai découvert que l'aspect le plus important de tout projet de logique programmable est un examen attentif des domaines d'horloge et des signaux de réinitialisation. Si ceux-ci sont correctement configurés, vous avez une bonne chance de faire fonctionner votre conception.

Pixel Clock et synchronisation verrouillés

Afin de vérifier que certains signaux sont actifs, c'est une bonne idée de lier ces signaux à des LED (horloges, réinitialisations, verrous, etc.). Deux signaux que j'ai trouvé utiles pour suivre sur la carte de l'émetteur étaient l'horloge de pixel et le signal "verrouillé" sur le bloc AXI4-Stream vers sortie vidéo, qui vous indique que la synchronisation vidéo a été synchronisée avec le contrôleur de synchronisation et la source vidéo Les données. J'ai ajouté une logique au wrapper du bloc de conception qui suit l'horloge des pixels en utilisant le signal PixelClkLocked sur le bloc dvi2rgb comme réinitialisation. J'ai joint le fichier en tant que hdmi_wrapper.v ici. Le fichier des contraintes est également joint ici.

Étape 2: Configurer la logique programmable Zynq pour le récepteur

Le bloc Logique Programmable pour le récepteur est plus simple. La principale différence, outre les blocs d'entrée HDMI manquants, est l'absence d'horloge de pixel récupérée. Pour cette raison, nous devons générer le nôtre à partir de l'assistant d'horloge. Cette conception doit être effectuée dans un projet distinct de l'émetteur. Pour nos besoins, le projet de récepteur a suivi la carte Zybo 7Z-20 tandis que l'émetteur a suivi la carte Z7-10. Les FPGA sur les cartes sont différents alors… soyez prudent.

Voici les étapes pour créer le bloc de conception du récepteur:

-

Ajoutez les blocs IP suivants à votre conception:

- Contrôleur de synchronisation

- AXI4-Stream vers sortie vidéo

- RVB vers DVI

- AXI VDMA

- AXI GPIO

- Système de traitement

- Assistant d'horloge

- Constante (VDD réglé sur 1)

- Suivez le même schéma pour configurer ces blocs que l'émetteur. Des images des différences notables de configuration ont été incluses ici. Les autres restent les mêmes que l'émetteur.

- Configurez le VDMA pour cette conception en tant que canal de lecture uniquement. Désactivez le canal d'écriture.

-

L'assistant d'horloge doit être configuré pour les sorties suivantes:

- clk_out1: 75 MHz (horloge de pixels)

- clk_out2: 150 MHz (horloge de flux)

- clk_out3: 50 MHz (horloge axi-lite)

- Connectez les blocs vidéo comme indiqué dans l'image de conception du bloc RX.

- Exécutez ensuite l'automatisation de la connexion, qui ajoutera les blocs AXI Interconnect, AXI SmartConnect et System Reset et tentera d'établir les connexions appropriées. Allez-y doucement pour vous assurer qu'il n'effectue pas de connexions indésirables.

- Rendre l'horloge HDMI TMDS et les broches de données externes sur le bloc rgb2dvi

- Pas besoin de signal de connexion à chaud sur cette conception.

Étape 3: configuration du pilote VDMA

La configuration des différents blocs configurés via l'interface AXI-Lite est mieux effectuée en utilisant les projets de démonstration inclus avec le BSP comme référence. Après avoir exporté le matériel de conception et lancé le SDK depuis Vivado, vous souhaiterez ajouter un nouveau package de support de carte et inclure la bibliothèque lwip202 dans la fenêtre des paramètres BSP. Ouvrez le fichier system.mss du BSP et vous verrez les pilotes de périphériques présents à partir de votre conception de bloc. L'option "Importer des exemples" vous permet d'importer des projets de démonstration qui utilisent ces périphériques et vous montre ainsi comment les configurer dans le logiciel à l'aide des pilotes Xilinx disponibles (voir image ci-jointe).

C'était la méthode utilisée pour configurer le VDMA, la minuterie et l'interruption et le GPIO. Le code source pour la transmission et la réception a été inclus ici. Les différences sont presque exclusivement dans main.c.

***REMARQUE: Étant donné que le système n'est pas entièrement fonctionnel au moment de la rédaction de ce didacticiel, le code source de cette section n'inclut pas le code du réseau sans fil. Plusieurs bogues doivent être résolus en raison de la combinaison des projets de transmission/réception du noyau vidéo avec les projets de transmission/réception du réseau. Par conséquent, ce tutoriel les traite séparément pour le moment.***

Fonction de gestionnaire d'interruption TX (IRQHandler)

Cette fonction lit les codes gray fournis par les VDMA de lecture et d'écriture via les blocs GPIO. Les codes de gris sont convertis en décimaux et utilisés pour sélectionner l'emplacement de mémoire de base de trame de la trame actuelle. La trame copiée est la trame précédente à celle écrite par le VDMA (par exemple, si le VDMA écrit dans la trame 2, nous copions la trame 1; si nous écrivons dans la trame 0, nous enveloppons et lisons à partir de la trame 2).

La fonction ne capture que toutes les 6 images pour réduire la fréquence d'images à 10 Hz au lieu de 60 Hz. La limite supérieure du réseau est de 300 Mbps. À 10 images par seconde, une bande passante de 221,2 Mbps est requise.

Commenter/dé-commenter deux lignes dans cette fonction permettra à l'utilisateur de passer en mode passthru HDMI à des fins de débogage/test (le code est commenté pour indiquer les lignes appropriées). Il copie actuellement la trame dans un emplacement mémoire utilisé par le code Ethernet.

Fonction de gestionnaire d'interruption RX (IRQHandler)

Cette fonction est très similaire à la fonction TX, mais elle copie à partir d'un FIFO à 2 tampons utilisé par l'Ethernet pour écrire les données entrantes. Le code Ethernet indique dans quelle trame est écrite de la FIFO, les données sont copiées à partir de la trame opposée. Les données sont copiées dans la trame directement derrière celle qui est lue par le VDMA pour éviter les déchirures.

Étape 4: Configurer le réseau de nanorouteurs

Afin de créer un réseau à l'aide des nanorouteurs TPlink, allumez-les individuellement et connectez-vous au SSID wifi par défaut des appareils. Vous trouverez plus d'informations sur les paramètres de configuration de cet appareil particulier dans le manuel d'utilisation de l'appareil.

Configurez l'un des appareils en tant que point d'accès, il servira de connexion principale pour le réseau. Assurez-vous de nommer le réseau et notez le nom, et désactivez DHCP (nous ne voulons pas que le routeur configure les adresses IP de manière dynamique, nous voulons que les cartes Zybo émettrice et réceptrice définissent elles-mêmes leurs adresses IP afin qu'elles soient cohérentes). Après la configuration, assurez-vous que l'appareil redémarre et établit ce réseau.

Configurez l'autre appareil en tant que client et assurez-vous qu'il se connecte au réseau SSID que vous avez configuré avec le premier nanorouteur. Encore une fois, assurez-vous que DHCP est désactivé pour le client.

Une fois que le client a terminé et redémarré, il doit se connecter au nanorouteur du point d'accès (si ce n'est pas le cas, il y a probablement un problème dans la configuration de l'un des appareils). Vous remarquerez que le voyant LED sur le client sera fixe une fois qu'il sera connecté au point d'accès.

Le voyant du nanorouteur du point d'accès continuera probablement à clignoter à ce stade, ce n'est pas grave ! Le voyant clignotant signifie qu'il n'est pas connecté à un autre appareil à partir de son port Ethernet, et une fois connecté à un Zybo configuré, la LED restera fixe indiquant une connexion réseau réussie.

Maintenant que nous avons configuré nos nanorouteurs, nous avons un réseau sans fil qui nous permettra de communiquer. Une note importante est que notre méthode de configuration pour les nanorouteurs (en tant que point d'accès et client) nous permet de communiquer de la carte Zybo émettrice à la carte Zybo réceptrice comme si les deux étaient connectés avec un seul fil Ethernet. Cela rend la configuration de notre réseau moins difficile, car l'alternative comprendrait probablement la configuration des cartes Zybo pour se connecter explicitement au serveur avec la connexion prévue.

Une fois les deux appareils configurés, les nanorouteurs sont configurés et prêts à être implémentés dans votre réseau WIDI. Il n'y a pas d'appariement spécifique entre les nanorouteurs et les cartes Zybo, car le point d'accès ou le client fonctionnera pour le périphérique de transmission ou de réception.

Étape 5: Configurer le système de traitement Zynq pour la transmission de données via Ethernet

Afin de transmettre les données HDMI d'une carte Zybo à l'autre, nous devons incorporer un protocole Ethernet avec notre pilote VDMA. Notre objectif ici est de diffuser des images vidéo individuelles via le périphérique Ethernet du système de traitement, à un débit défini qui est compatible avec la bande passante de notre réseau. Pour notre projet, nous avons utilisé TCP fourni par l'API LwIP bare-metal. Étant donné que les deux membres du projet sont relativement inexpérimentés avec les utilitaires de réseau, ce choix a été fait sans pleinement reconnaître les implications et les contraintes impliquées avec TCP. Le problème majeur de cette implémentation était la bande passante limitée et le fait qu'elle n'est vraiment pas conçue dans le but de diffuser de gros volumes de données. Des solutions alternatives pour remplacer TCP et améliorer le tbe dans ce projet seront discutées plus tard.

Une brève description de TCP avec LwIP: Les données sont envoyées sur le réseau en paquets de taille tcp_mss (taille maximale de segment TCP), qui est généralement de 1460 octets. L'appel de tcp_write prendra certaines données référencées par un pointeur et configurera pbufs (tampons de paquets) pour contenir les données et fournir une structure pour les opérations TCP. La quantité maximale de données pouvant être mises en file d'attente à la fois est définie comme tcp_snd_buf (espace tampon de l'expéditeur TCP). Étant donné que ce paramètre est un nombre de 16 bits, nous sommes limités à une taille de tampon d'envoi de 59695 octets (il y a un remplissage requis dans le tampon d'envoi). Une fois les données mises en file d'attente, tcp_output est appelé pour commencer à transmettre les données. Avant d'envoyer le segment de données suivant, il est impératif que tous les paquets précédents aient été transmis avec succès. Ce processus est effectué à l'aide de la fonction recv_callback, car c'est la fonction qui est appelée lorsque l'accusé de réception est vu du récepteur.

L'utilisation des exemples de projets dans Vivado SDK est très utile pour apprendre le fonctionnement de LwIP TCP et constitue un bon point de départ pour commencer un nouveau projet.

La procédure pour l'appareil émetteur WiDi est la suivante:

- Initialisez le réseau TCP à l'aide des appels de fonction du pilote LWIP sans système d'exploitation.

- Spécifiez les fonctions de rappel nécessaires pour les opérations réseau.

- Connectez-vous au récepteur WiDi en vous connectant à son adresse IP et à son port (notre configuration: l'IP du récepteur est 192.168.0.9, connectez-vous au port 7).

- Lorsque la minuterie du pilote VDMA expire, entrez l'ISR TX.

- Déterminer le tampon de trame actuel auquel accéder en fonction du code gray VDMA

- Mettre en file d'attente le premier segment de données dans le tampon d'envoi TCP

- Sortez les données et mettez à jour les variables locales pour garder une trace de la quantité de données envoyées de la trame actuelle.

- Après avoir atteint le rappel reçu (appel de fonction effectué après que l'émetteur a reçu un accusé de réception de la récupération des données), mettre en file d'attente le segment de données suivant.

- Répétez les étapes 7 et 8 jusqu'à ce que la trame entière ait été envoyée.

- Revenez à un état inactif pour attendre la prochaine interruption du temporisateur pour indiquer qu'une nouvelle trame est prête (Retour à l'étape 4).

Assurez-vous de configurer les paramètres LwIP du package de support de carte comme indiqué dans l'image ci-dessus. Toutes les valeurs sont par défaut sauf tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Notez également qu'un débogage détaillé peut être réalisé en modifiant les paramètres BSP pour le groupe debug_options.

Étape 6: Configurer le système de traitement Zynq pour la réception de données via Ethernet

La carte de développement Zybo qui servira de récepteur sans fil fonctionnera de la même manière que l'appareil émetteur. Les paramètres du package de support de carte pour LwIP seront identiques à ceux de l'étape précédente.

L'appareil prendra en charge les paquets contenant les segments de trame vidéo du nanorouteur et copiera les données de trame vidéo dans l'espace tampon triple trame pour le VDMA de réception. Afin d'éviter d'écraser des données, un double tampon de données (que nous appellerons le tampon réseau) est utilisé lors de la collecte de données à partir du nanorouteur, afin que le trafic réseau puisse continuer à être diffusé pendant que l'image vidéo complète précédente est copiée dans le Tampon VDMA.

La procédure pour le périphérique de réception WiDi nécessite deux tâches, l'une consistant à recevoir des données Ethernet et l'autre à copier des images vidéo du tampon réseau vers le tampon triple trame du VDMA.

Tâche de réception Ethernet:

- Initialisez le réseau TCP à l'aide des appels de fonction du pilote LWIP bare-metal (configuration avec l'adresse IP à laquelle l'émetteur se connectera, 192.168.0.9 dans le nôtre)

- Spécifiez les fonctions de rappel nécessaires pour les opérations réseau.

- Une fois le paquet Ethernet reçu, copiez les données du paquet dans la mémoire tampon du réseau actuel, augmentez les données accumulées actuelles.

- Si le paquet remplit le tampon de trame réseau, passez aux étapes 5 et 6. Sinon, revenez à l'étape 3 pour cette tâche.

- signaler que la tâche de mémoire tampon à triple trame VDMA doit copier à partir de la mémoire tampon de réseau nouvellement terminée.

- Basculez vers l'autre tampon réseau et continuez à collecter des données via Ethernet.

- Idle jusqu'à ce qu'un nouveau paquet Ethernet soit reçu (étape 3).

Copiez le tampon réseau dans le tampon triple trame VDMA:

- Lorsque le minuteur du pilote VDMA expire, entrez le RX ISR.

- Déterminez le tampon de trame actuel auquel accéder en fonction du code gray VDMA.

- Déterminez quel tampon réseau sera copié dans le tampon VDMA et copiez ces données

Étape 7: connectez vos cartes Zybo à la source HDMI et à l'évier HDMI

Connectez maintenant les câbles HDMI pour le récepteur et l'émetteur, programmez les FPGA et exécutez le système de traitement. La fréquence d'images sera probablement très lente, en raison de l'immense surcharge du fonctionnement LwIP et de la bande passante limitée. En cas de problème, connectez-vous via UART et essayez d'identifier les avertissements ou les erreurs.

Étape 8: Idées alternatives d'amélioration

Un gros problème pour ce projet était la quantité de données nécessaires pour envoyer via le wifi. C'était prévu, mais nous avons sous-estimé l'impact que cela aurait et résulté en une rafale d'images sur un écran plutôt qu'un flux vidéo. Il y a plusieurs façons d'améliorer ce projet:

- Compression vidéo en temps réel. La compression du flux vidéo entrant image par image réduirait considérablement la quantité de données à envoyer sur le réseau. Idéalement, cela serait fait dans le matériel (ce qui n'est pas une tâche facile), ou cela pourrait être fait dans le logiciel en utilisant l'autre noyau ARM pour exécuter des algorithmes de compression (cela nécessiterait une analyse plus approfondie pour s'assurer que le timing fonctionne). Il existe des composants de compression vidéo en temps réel open source que nous avons trouvés sur le Web, mais la majorité sont IP.

- Implémentation du flux Ethernet dans le matériel plutôt que dans le logiciel. Il y avait une tonne de surcharge en raison du manque d'espace disponible pour mettre en file d'attente les données sortantes dans l'émetteur, en raison de la limitation de la taille du segment. Un processus beaucoup plus efficace consiste à utiliser l'IP Ethernet AXI avec un tampon FIFO ou un DMA pour y alimenter des données. Cela réduirait le bagage supplémentaire de LwIP TCP et permettrait un plus grand flux de données.

Étape 9: Accessibilité

Le produit résultant de ce projet WiDi devrait être une paire d'appareils compacts et entièrement intégrés qu'un utilisateur pourrait connecter à n'importe quelle source HDMI, puis transférer le flux vidéo vers un écran avec capacité HDMI sans fil. Les appareils comporteraient le SoC Zynq-7000 trouvé sur la carte de référence Zybo et incorporeraient le matériel réseau trouvé dans les nano-routeurs TP-Link. Idéalement, l'utilisateur serait capable de contrôler le module de transmission à partir d'un emplacement discret au sein du système d'exploitation cible, avec peu de besoin d'une capacité technique significative.

Sécurité et connectivité

Les appareils doivent également intégrer Transport Layer Security (TLS) et avoir une capacité de connexion automatique limitée, à la fois pour des raisons de confidentialité. Les concepteurs ont l'intention de faire de la connexion avec un écran via une interface sans fil une action délibérée de la part de l'utilisateur afin d'éviter de diffuser par erreur du matériel sensible.

Statut actuel

Jusqu'à présent, l'état du projet est encore en grande partie un travail en cours. Pour que l'utilisateur final actuel puisse bénéficier de ce didacticiel, il doit avoir une solide compréhension technique de la conception de systèmes embarqués et doit avoir une certaine familiarité avec le matériel programmable et les logiciels embarqués fonctionnant ensemble.

Les données envoyées sur le réseau ne sont pas cryptées à ce stade et sont supposées être une transmission brute de paquets TCP/IP.

Le projet de base vidéo a été testé avec succès pour la transmission et la réception. D'autre part, la connexion sans fil entre deux cartes zybo a été établie et les données de trame de test ont été envoyées avec succès. Il reste cependant nécessaire de combiner le code réseau à chaque projet de cœur vidéo et de tester la transmission des trames vidéo réelles.

Conseillé:

Robot Arduino sans fil utilisant le module sans fil HC12 : 7 étapes

Robot Arduino sans fil utilisant le module sans fil HC12 : Salut les gars, bon retour. Dans mon article précédent, j'ai expliqué ce qu'est un circuit de pont en H, un circuit intégré de pilote de moteur L293D, un circuit de pilote de moteur L293D superposé pour piloter des pilotes de moteur à courant élevé et comment vous pouvez concevoir et fabriquer votre propre carte de pilote de moteur L293D

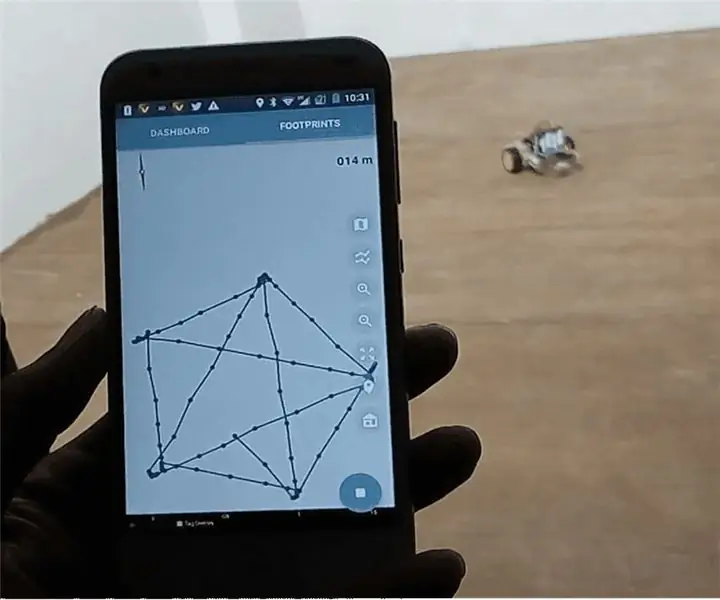

Robot de navigation avec capteurs de chaussures, sans GPS, sans carte : 13 étapes (avec photos)

Robot de navigation avec capteurs de chaussures, sans GPS, sans carte : le robot se déplace selon une trajectoire préprogrammée et transmet (via Bluetooth) ses informations de mouvement réelles à un téléphone pour un suivi en temps réel. Arduino est préprogrammé avec chemin et oblu est utilisé pour détecter le mouvement du robot. oblu transmet les informations de mouvement

Point d'accès sans fil de 50 mètres de portée avec adaptateur sans fil USB TP Link WN7200ND sur Raspbian Stretch: 6 étapes

Point d'accès sans fil de 50 mètres de portée avec adaptateur sans fil USB TP Link WN7200ND sur Raspbian Stretch : Raspberry Pi est idéal pour créer des points d'accès sans fil sécurisés mais il n'a pas une bonne portée, j'ai utilisé un adaptateur sans fil USB TP Link WN7200ND pour l'étendre. Je veux partager comment le fairePourquoi est-ce que je veux utiliser un Raspberry Pi au lieu d'un routeur ?T

Quadcopter utilisant la carte Zybo Zynq-7000 : 5 étapes

Quadcopter utilisant la carte Zybo Zynq-7000 : Avant de commencer, voici quelques éléments que vous souhaitez pour le projet : Liste des pièces 1 x carte Digilent Zybo Zynq-7000 1 x cadre quadrirotor capable de monter Zybo (fichier Adobe Illustrator pour la découpe au laser joint) 4 x Turnigy D3530/ 14 Moteurs Brushless 1100KV 4x

Système DIY de micro sans fil pour guitare sans fil : 4 étapes

DIY Wireless Mic to Wireless Guitar System: J'ai regardé des vidéos et des groupes et presque tous utilisent un système sans fil à la guitare. Devenir fou, bouger, marcher et faire ce qu'ils veulent sans le cordon alors je rêve d'en avoir un.. Mais.. pour moi maintenant c'est trop cher alors je suis arrivé à ça