Table des matières:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:09.

- Dernière modifié 2025-01-23 14:46.

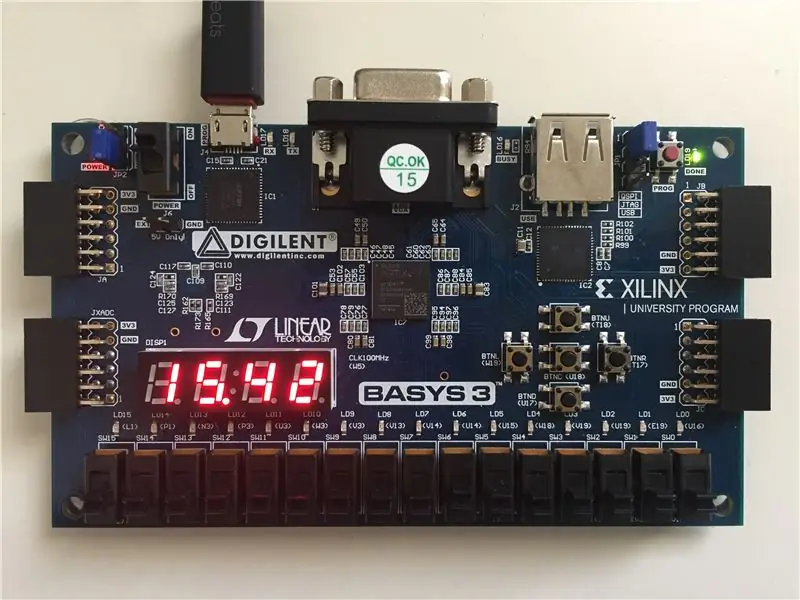

Il s'agit d'un didacticiel sur la façon de créer un chronomètre à l'aide de VHDL et d'une carte de circuit imprimé FPGA, comme une carte Basys3 Atrix-7. Le chronomètre est capable de compter de 00,00 secondes à 99,99 secondes. Il utilise deux boutons, un pour le bouton marche/arrêt et un autre pour le bouton de réinitialisation. Les chiffres sont affichés sur l'affichage à sept segments de la carte à l'aide de ses anodes et cathodes. Trois fichiers différents sont nécessaires pour que ce chronomètre fonctionne.

Étape 1: Matériel/Logiciel

- Carte FPGA Basys3 Atrix-7

- Suite Vivado Design de Xilinx

- USB 2.0 A mâle vers Micro-B mâle

Étape 2: Schéma fonctionnel

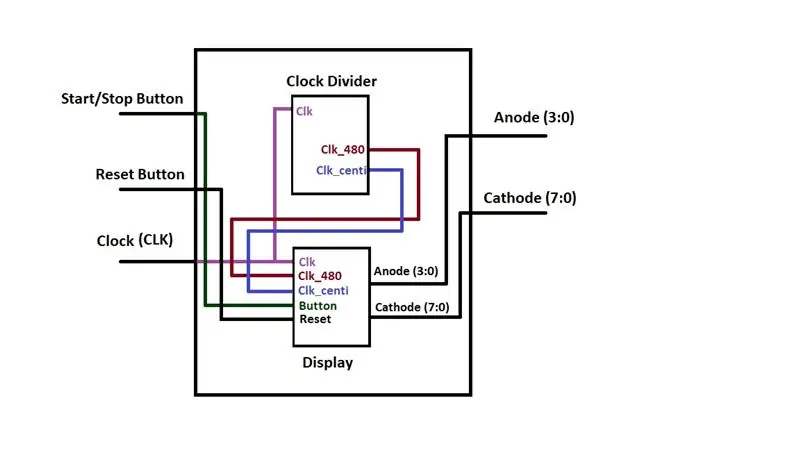

Le chronomètre global a trois entrées et deux sorties. Les trois entrées sont le démarrage/arrêt, la réinitialisation et l'horloge. Le démarrage/arrêt et la réinitialisation sont des boutons et l'horloge est l'horloge 100MHz de la carte. Les deux sorties sont les anodes et les cathodes de l'affichage à sept segments.

Le premier module (diviseur d'horloge) a une entrée et deux sorties. L'entrée est l'horloge 100 MHz de la carte et les sorties sont deux horloges distinctes, l'une fonctionnant à 480 Hz et l'autre à 0,5 MHz.

Le deuxième module (affichage) a cinq entrées et deux sorties. Les entrées sont l'horloge 100 MHz de la carte, les deux horloges du module diviseur d'horloge et les boutons marche/arrêt et réinitialisation. Les sorties sont les anodes et les cathodes.

Le dernier module (modélisé par l'ensemble du schéma fonctionnel) possède trois entrées et deux sorties. C'est le fichier qui rassemble tout. Les entrées sont les 100MHz de la carte et les boutons marche/arrêt et réinitialisation. Les sorties sont les anodes et les cathodes qui contrôlent l'affichage à sept segments. Toutes les entrées et sorties sont physiquement sur la carte pour le module final.

Étape 3: Diagramme d'état

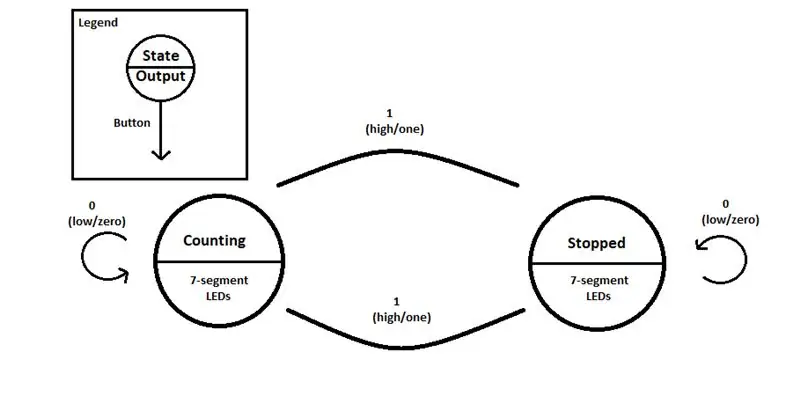

L'image ci-dessus montre le diagramme d'état du fonctionnement du chronomètre. Appuyer sur le bouton de réinitialisation n'a aucun effet sur l'état du chronomètre. L'état suivant est déterminé par le bouton marche/arrêt. Le démarrage/arrêt est "HIGH" lorsqu'il est enfoncé, mais pas lorsqu'il est maintenu enfoncé, et "LOW" lorsque le bouton a rebondi ou a été maintenu enfoncé après avoir été momentanément "HIGH".

Si le chronomètre compte et que le bouton marche/arrêt passe à « HIGH », alors il arrête de compter. Si le chronomètre est arrêté et que le bouton marche/arrêt passe à « HIGH », il recommence à compter. Pour les deux états, si le bouton marche/arrêt est "LOW", alors il restera dans l'état dans lequel il se trouve actuellement.

Étape 4: Module de diviseur d'horloge

Le module diviseur d'horloge a une entrée, l'horloge 100 MHz de la carte, et deux sorties, les horloges 480 Hz et 0,5 MHz. L'horloge de 480 Hz est utilisée pour maintenir toutes les LED de l'affichage à sept segments « allumées » en même temps en passant rapidement d'une des quatre à l'autre. L'horloge à 0,5 MHz est utilisée pour que le chronomètre compte réellement par centi-secondes.

Étape 5: Module d'affichage

Ce module d'affichage a cinq entrées, l'horloge 100MHz de la carte, les deux horloges du module d'horloge et les boutons marche/arrêt et réinitialisation, et deux sorties, les anodes et les cathodes. Ce module a également la "logique" de la façon dont le chronomètre compte et intègre la machine à états finis.

Étape 6: module de liaison

Ce dernier module est celui qui rassemble les deux autres modules. Il a trois entrées, l'horloge 100MHz de la carte et les boutons marche/arrêt et réinitialisation, et deux sorties, les anodes et les cathodes. L'horloge 100MHz va au module diviseur d'horloge et au module d'affichage, et les boutons marche/arrêt et réinitialisation vont au module d'affichage. Les sorties du module diviseur d'horloge (480 Hz et 0,5 MHz) vont aux deux entrées d'horloge du module d'affichage. Les sorties du module d'affichage (anodes et cathodes) vont vers les sorties du module final.

Étape 7: Contraintes

Les deux entrées peuvent être n'importe quel bouton de la carte FPGA Basys3 Atrix-7 et les sorties seront les quatre anodes et les huit cathodes (car vous voulez également un point décimal entre les secondes et les millisecondes) pour l'affichage à sept segments.

Étape 8: terminé

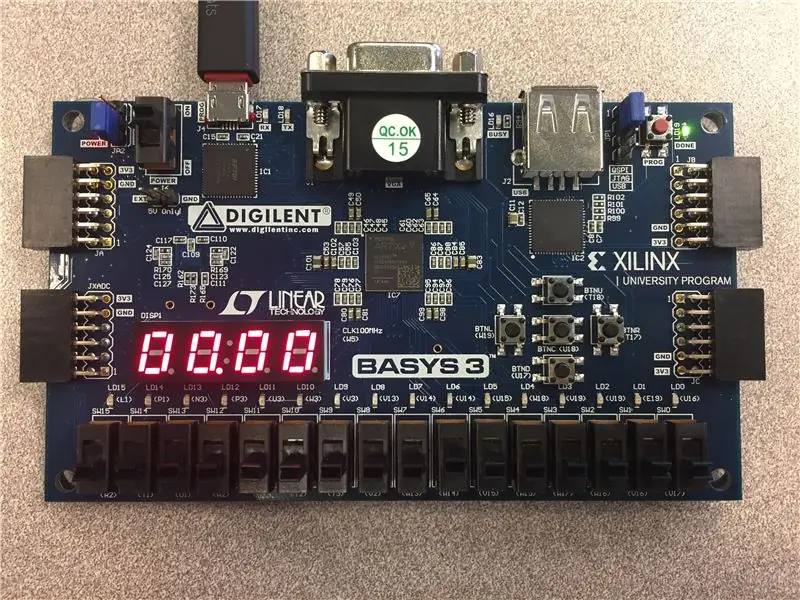

Téléchargez le programme sur votre carte FPGA Basys3 Atrix-7 et appuyez sur votre bouton marche/arrêt pour lancer le chronomètre !

Conseillé:

Chronomètre des Croakers : 16 étapes (avec photos)

Chronomètre des Croakers : Si vous souriez aux grenouilles, certaines d'entre elles vibreront. En comprenant le mouvement, on peut lire l'heure - une opération instable. Les grenouilles « relèvent les yeux » représentent les heures en binaire (de gauche à droite; 8,4,2,1). représentent min

Chronomètre numérique tout en un (horloge, minuterie, alarme, température): 10 étapes (avec photos)

Chronomètre numérique tout-en-un (horloge, minuterie, alarme, température) : nous prévoyions de faire une minuterie pour une autre compétition, mais plus tard nous avons également mis en place une horloge (sans RTC). Au fur et à mesure que nous nous sommes lancés dans la programmation, nous nous sommes intéressés à appliquer plus de fonctionnalités à l'appareil et avons fini par ajouter le DS3231 RTC, comme

Comment faire un chronomètre à l'aide d'Arduino : 8 étapes (avec photos)

Comment faire un chronomètre à l'aide d'Arduino : il s'agit d'un chronomètre à écran LCD Arduino 16 * 2 très simple ……… Si vous aimez cette instruction, veuillez vous abonner à ma chaîne https://www.youtube.com /ZenoModiff

Chronomètre de base utilisant VHDL et carte Basys3 : 9 étapes

Chronomètre de base à l'aide de VHDL et de la carte Basys3 Nous sommes ravis de partager notre projet avec vous! Il s'agissait d'un projet final pour le cours CPE 133 (Design numérique) à Cal Poly, SLO à l'automne 2016. Le projet que nous construisons

Chronomètre d'une minute VHDL : 5 étapes

Chronomètre d'une minute VHDL : il s'agit d'un didacticiel sur la façon de créer un chronomètre d'une minute à l'aide de VHDL et d'une carte Basys 3. Un tel appareil est idéal pour les jeux où chaque joueur dispose d'une minute maximum pour jouer son rôle. Le chronomètre affiche avec précision les secondes et les millisecondes o