Table des matières:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:05.

- Dernière modifié 2025-01-23 14:45.

Par AmCoderhttps://www.linkedin.com/in/mituFollow Plus par l'auteur:

À propos de: Mitu Raj -- Juste un amateur et un apprenant -- Concepteur de puces -- Développeur de logiciels -- Passionné de physique et de mathématiques En savoir plus sur AmCoder »

## Ceci est le lien le plus cliqué et le plus populaire de Google pour l'implémentation VHDL de l'ALGORITHME CORDIC pour générer des ondes sinus et cosinus## À l'heure actuelle, il existe de nombreux algorithmes efficaces pour le matériel, mais ceux-ci ne sont pas bien connus en raison de la prédominance des systèmes logiciels sur les nombreuses années. CORDIC est un tel algorithme qui n'est rien d'autre qu'un ensemble de logiques de décalage et d'addition utilisées pour calculer un large éventail de fonctions, y compris certaines fonctions trigonométriques, hyperboliques, linéaires et logarithmiques. C'est l'algorithme utilisé dans les calculatrices, etc. Ainsi, en utilisant simplement de simples décalages et additionneurs, nous pouvons concevoir un matériel avec moins de complexité mais la puissance du DSP en utilisant l'algorithme cordic. Par conséquent, il peut être conçu comme une conception RTL nue en VHDL ou Verilog sans utiliser d'unités à virgule flottante dédiées ou d'adresses IP mathématiques complexes.

Étape 1: VHDL et Modelsim

Ici, l'algorithme cordic est implémenté en utilisant VHDL pour générer une onde sinusoïdale et une onde cose. Il peut produire le sinus et le cosinus de l'angle d'entrée avec une grande précision. Le code est synthétisable sur FPGA. Modelsim est utilisé pour simuler la conception et le banc d'essai.

Étape 2: Code VHDL pour la conception et le banc de test

La technique de mise à l'échelle binaire est utilisée pour représenter les nombres à virgule flottante.

Veuillez consulter les documents joints avant de coder.

Passez en revueSimulation cordic_v4.vhd - La conception -L'entrée est l'angle en 32 bits + bit de signe; il peut traiter n'importe quel angle de 0 à +/-360 degrés avec une précision d'entrée de 0,000000000233 degrés. Lorsque vous donnez l'entrée -> MSB est le bit de signe et les 32 bits restants représentent la magnitude.-La sortie de la conception est sa valeur sinus et cos en 16 bits + bit de signe. avec une précision de 0,00001526. Veuillez noter que la sortie est affichée sous forme de complément 2 si la valeur sinus ou cos respective est négative. Simulation de testb.vhd - Banc d'essai pour la conception (1) Angles d'entrée et réinitialisation de traction = '0'. Après deux étapes de simulation, réinitialisez à '1' et "exécutez tout".(2) Dans la fenêtre de simulation, définissez la base des signaux sin et cos comme décimal et format > Analogique (automatique).(3) Effectuez un zoom arrière pour voir la forme d'onde correctement.

Étape 3: Fichiers joints

(1) cordic_v4.vhd - Conception.(2) testb.vhd - Banc d'essai pour la conception.

(3) Documenter sur la façon de forcer les entrées d'angle et de convertir les résultats binaires.

Mise à jour: CES FICHIERS SONT OBSÉLÉTÉS ET NE FOURNISSENT PLUS. VEUILLEZ UTILISER LES FICHIERS DE L'ÉTAPE SUIVANTE

Étape 4: Mini-Cordic IP Core - 16 bits

La limitation de la mise en œuvre ci-dessus est lente, fréquence d'horloge inférieure en raison des calculs effectués en un seul cycle d'horloge. Mini-Cordic IP Core - 16 bits

- Chemins critiques répartis sur plusieurs cycles pour améliorer les performances.- Plus rapide - Conception éprouvée FPGA synthétisée jusqu'à une horloge de 100 Mhz.- Plus de zone optimisée en HDL, matériel moindre.- Signaux Load et Done Status ajoutés.- Seul inconvénient est une résolution inférieure par rapport au précédent. Banc d'essai:

complètement automatisé des entrées d'angle de 0 à 360 degrés

Fichiers joints: 1) fichier vhdl principal mini cordic2) banc d'essai mini cordic3) manuel Mini Cordic IP Core4) Doc sur la façon de forcer les angles et de convertir les résultats

Pour toute question, n'hésitez pas à me contacter:

Mitu Raj

suivez-moi:

courrier: iammituraj@gmail.com

###Téléchargements totaux: 325 au 01-05-2021###

### Dernière modification du code: 2020-07-07 ###

Conseillé:

Robot auto-équilibrant - Algorithme de contrôle PID : 3 étapes

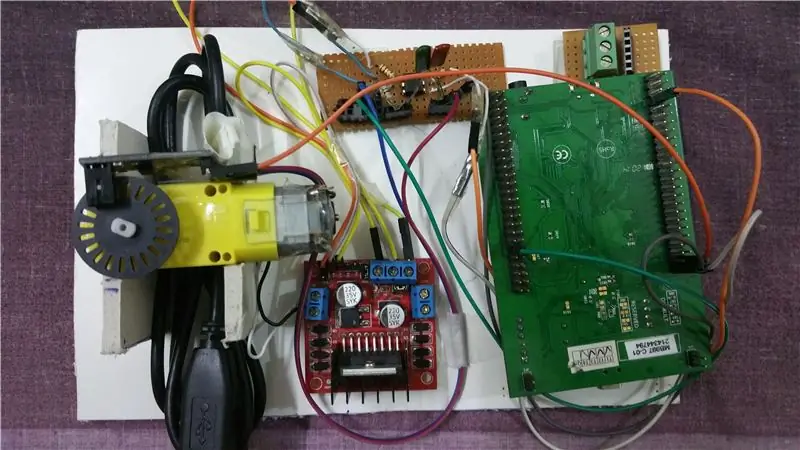

Robot à équilibrage automatique - Algorithme de contrôle PID : Ce projet a été conçu parce que je souhaitais en savoir plus sur les algorithmes de contrôle et sur la manière de mettre en œuvre efficacement des boucles PID fonctionnelles. Le projet est encore en phase de développement car un module Bluetooth n'a pas encore été ajouté qui sera al

Intelligence artificielle des jeux de société : l'algorithme Minimax : 8 étapes

Intelligence artificielle des jeux de société : l'algorithme Minimax : Vous êtes-vous déjà demandé comment sont fabriqués les ordinateurs contre lesquels vous jouez aux échecs ou aux dames ? Eh bien, ne cherchez pas plus loin que ce Instructable car il vous montrera comment créer une intelligence artificielle (IA) simple mais efficace à l'aide de l'algorithme Minimax ! En utilisant le

Robot à équilibrage automatique utilisant l'algorithme PID (STM MC): 9 étapes

Robot à équilibrage automatique utilisant l'algorithme PID (STM MC) : Récemment, de nombreux travaux ont été effectués sur l'équilibrage automatique des objets. Le concept d'auto-équilibrage a commencé avec l'équilibrage du pendule inversé. Ce concept s'est également étendu à la conception d'avions. Dans ce projet, nous avons conçu un petit mod

Tic Tac Toe sur Arduino avec AI (algorithme Minimax): 3 étapes

Tic Tac Toe sur Arduino avec IA (algorithme Minimax) : dans ce Instructable, je vais vous montrer comment créer un jeu de Tic Tac Toe avec une IA à l'aide d'un Arduino. Vous pouvez soit jouer contre l'Arduino, soit regarder l'Arduino jouer contre lui-même. J'utilise un algorithme appelé "algorithme minimax"

Contrôle de la vitesse du moteur à courant continu à l'aide de l'algorithme PID (STM32F4) : 8 étapes (avec images)

Contrôle de la vitesse du moteur à courant continu à l'aide de l'algorithme PID (STM32F4) : bonjour à tous, voici tahir ul haq avec un autre projet. Cette fois, c'est STM32F407 en tant que MC. Il s'agit d'un projet de fin de semestre. J'espère que vous l'aimez. Cela nécessite beaucoup de concepts et de théorie, alors nous y allons d'abord. Avec l'avènement des ordinateurs et de la