Table des matières:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:05.

- Dernière modifié 2025-01-23 14:45.

Dans le passé, j'ai écrit un guide sur la façon de construire un ordinateur basé sur Z80, et j'ai conçu le circuit pour être aussi simpliste que possible afin qu'il puisse être construit aussi facilement que possible. J'ai aussi écrit un petit programme en utilisant la même idée de simplicité. Cette conception a plutôt bien fonctionné, mais je n'en étais pas totalement satisfait. J'ai commencé par réécrire un programme qui lui permettait d'être programmé pendant l'exécution. Cela me permettait de tester des morceaux de code sans avoir à le dédier à l'EEPROM, ce qui m'obligerait à reprogrammer l'EEPROM. Cela ne me semblait pas une idée amusante. Ensuite, j'ai commencé à penser aux espaces mémoire. Si je voulais interfacer un morceau de matériel (IO principalement), un morceau de code pourrait potentiellement dépasser la quantité d'espace mémoire disponible pour le système. N'oubliez pas que la conception n'utilisait que l'octet inférieur du bus d'adresses, puis le bit inférieur de l'octet élevé était utilisé pour choisir entre les espaces ROM et RAM. Cela signifiait que je n'avais que 253 octets d'espace à utiliser. Vous demandez peut-être pourquoi 253 au lieu de 256. C'est parce que mon nouveau code injecte trois octets de données à la fin d'un programme écrit (cela sera couvert plus tard, car je l'ai modifié pour travailler sur le nouveau design).

m

Je suis revenu sur mes anciens schémas pour voir ce qui se passait d'autre. J'ai trouvé un petit défaut avec le circuit de sélection de mémoire, que je couvrirai quand j'y serai. La version simplifiée: toutes les demandes d'écriture passeraient en fait, bien qu'elles soient toujours mises en RAM. Cela ne valait probablement pas la peine de s'inquiéter, mais je voulais le faire correctement cette fois. Et avec ça, j'ai commencé à dessiner un nouveau schéma. Les deux photos jointes à cette page sont avant et après le circuit réel. J'ai tellement nettoyé le câblage des spaghettis, ce n'est pas drôle.

m

Si vous avez suivi ma soumission originale et prévoyez de suivre celle-ci, vous allez me détester. Si vous commencez à zéro, alors vous avez de la chance. Il suffit de saisir les pièces de la liste (ou leur équivalent) et de suivre.

Fournitures:

LM7805 - Régulateur 5 VoltZ80 - le CPU; le cerveau du systèmeAT28C64B - EEPROM. Stockage de données « permanent » utilisé pour le firmware de l'ordinateur IDT6116SA - SRAM; utilisé pour stocker le code utilisateur et/ou le stockage de données généralesNE555 - Horloge système74HC374 - Octal D-Latch avec /OE; utilisé comme puce d'entrée74LS273 - Octal D-Latch avec /MR; puce de sortieTLC59211 - Puce de pilote de LED (utilisée pour que le 74LS273 puisse piloter des LED, car elle seule n'est pas capable de la sortie de courant)MC14572 - Il s'agit d'une puce "Line Driver", mais je l'ai trouvée parfaite pour la logique de contrôle de la mémoire. Il dispose de 4 onduleurs et d'une porte NAND et NOR intégrée74LS32 - Quad OR gateCD4001 - Quad NOR gateCD4040 - Compteur d'ondulation à 12 étages; Diviseur d'horloge dessiné, mais non implémenté (pour faire fonctionner le système à des vitesses d'horloge plus lentes)2 Résistances 10K Ohm - Une est utilisée dans le circuit de minuterie 555, utilisez donc la valeur que vous souhaitez pour elle4 Résistances 1K Ohm - Une est utilisée pour le Circuit de minuterie 555, alors utilisez ce que vous voulez pour cela. Un autre est utilisé pour piloter les LED, donc variez-le aussi si vous le souhaitez 8x330 Ohm Resistor Bus8x10K Ohm Resistor Bus11 LED - Trois sont utilisés pour l'état du système et les huit autres sont des sorties. Pour le 8, j'ai utilisé un affichage graphique à barres (HDSP-4836) 4 condensateurs - Deux sont utilisés pour le LM7805; 0,22 uF et 0,1 uF. L'un est pour la minuterie 555, alors utilisez ce que vous pensez être juste. Le dernier est pour la réinitialisation à la mise sous tension; 100uF2 N. O. Boutons-poussoirs - L'un est utilisé pour l'entrée, l'autre pour la réinitialisation8 Commutateurs DIP SPST - Entrée de données; J'ai utilisé Piano Key styleWire. Beaucoup, beaucoup de fil

m

REMARQUE: la version à trou traversant MC14572 est obsolète, mais la version SMD est toujours active (pas même le statut « pas pour une nouvelle conception »), vous devrez donc peut-être acheter une carte de circuit imprimé pour vous permettre de l'utiliser. Un deuxième 74LS32 peut être utilisé à la place du MC14572 (se référer au schéma du "circuit de sélection de mémoire" de l'ible précédent)

Étape 1: Présentation rapide des modifications + Schémas

Comment lire les schémas:Une flèche pointée vers une puce est une entrée:Entrée >-Une flèche pointée loin d'une puce est une sortie:Sortie <-Les bus utilisent une ligne au lieu d'une flèche:Bus |-

m

La plupart des jetons ont été dessinés avec leurs brochages exacts. Le petit creux a été dessiné sur ces jetons. La plupart des puces ont également des numéros de broche et des étiquettes. Ils peuvent être un peu difficiles à lire. Mon crayon devenait terne.

m

En termes de connexions de circuits, la disposition de la nouvelle conception est pratiquement inchangée par rapport à l'original. J'ai connecté le quartet inférieur de l'octet de poids fort d'adresse aux mémoires, puis j'ai utilisé le bit de poids faible du quartet supérieur (A12) pour la sélection RAM/ROM. Cela signifie que l'espace ROM est passé de 0000-00FF à 0000-0FFF. L'espace RAM est passé de 0100-01FF à 1000-1FFF. J'ai également échangé la logique de contrôle de la mémoire pour une meilleure conception et ajouté deux nouvelles LED d'état (et une logique de colle). J'ai également dessiné (mais pas câblé) un circuit diviseur d'horloge. Il devait remplir deux fonctions. La fonction évidente est de diviser la fréquence d'horloge vers le bas. L'autre fonction est à des fins PWM (Pulse Width Modulation), car le 555 ne génère pas d'ondes avec des cycles de service de 50%. Cela n'a pas vraiment d'importance dans ce circuit, mais si vous deviez utiliser l'horloge pour piloter certaines LED, vous remarquerez certainement les effets (une (ensemble de) LED sera plus faible que l'autre). L'ensemble du reste du circuit est essentiellement inchangé.

Étape 2: CPU, mémoire et contrôle de la mémoire

C'est la partie où les lecteurs de ma version précédente me détestent. Dans la construction d'origine, j'ai juste jeté des pièces sur la carte à un endroit où elles semblaient poser peu de problèmes de câblage. Le résultat donnait l'impression que quelqu'un avait jeté une assiette de spaghetti dessus et ressemblait à des « fils ! » Je voulais le nettoyer un peu, alors j'ai commencé par tout déchirer sauf le CPU, la RAM et la ROM. J'ai extrait presque tout le circuit d'entrée, le circuit de sortie et la logique de la colle. Cela me faisait presque mal de le faire, mais c'était nécessaire. J'ai laissé toutes les connexions de données intactes et l'octet inférieur du bus d'adresse. J'ai ensuite connecté les quatre bits suivants du bus d'adresse (A8-A11) à la puce ROM. J'ai pris soin de faire le tour de la puce cette fois pour la rendre plus facile à remonter pour la reprogrammation. J'ai également sauté les connexions d'adresse vers la puce RAM.

m

Avec cela à l'écart, je devais maintenant brancher la logique de contrôle de la mémoire. Dans le schéma d'origine, j'avais connecté la ligne /MREQ du processeur directement à /CE aux deux puces de mémoire, puis j'avais câblé /WR aux RAM /WE. Ensuite, j'ai eu les CPU /RD et /MREQ logiquement OR ensemble ainsi que A9. Essentiellement, il a été configuré de manière à ce que toutes les demandes de mémoire activent à la fois la RAM et la ROM, mais A9 a été utilisé pour sélectionner le / OE des puces sélectionné. C'était bien et tout cela parce que les puces resteraient inactives jusqu'à ce qu'une demande de mémoire soit faite et alors un seul /OE serait actif pendant une demande de lecture. Cela a empêché la diaphonie, mais a introduit une nuance gênante. Parce que A9 n'était utilisé que pour déterminer quelle puce produisait des données et parce que le processeur avait un accès direct à la broche /WE de la RAM, toutes les demandes d'écriture seraient traitées. C'était correct pour la ROM car son mode d'écriture est inhibé en liant /WE directement à l'alimentation 5V. La RAM, cependant, serait écrite indépendamment de A9. Cela signifiait qu'une tentative d'écriture dans un emplacement de l'espace ROM écrirait au même emplacement dans l'espace RAM.

m

Une solution pour cela serait de recâbler la logique de contrôle afin que le processeur ait un accès direct aux broches /OE et /WE des puces, puis d'utiliser MREQ et A12 pour sélectionner les puces /CE qui ont été pilotées. J'ai opté pour cette idée, mais au lieu d'utiliser quatre portes NOR et un onduleur comme la conception d'origine, j'ai trouvé une petite puce maladroite qui était parfaite pour la tâche. J'ai dû créer un circuit qui n'utilisait que les portes logiques disponibles dans la puce, mais c'était assez facile. A12 alimente directement une porte NAND et une porte NOR. /MREQ est introduit dans la porte NOR et son complément est introduit dans la porte NAND. La porte NAND est utilisée pour piloter /CE pour la RAM et la sortie NOR est inversée et utilisée pour piloter la ROM /CE. Cela fait en sorte que /MREQ doit être faible avant que l'une ou l'autre des puces ne soit sélectionnée, puis A12 choisit celle qui est sélectionnée. Avec cette configuration, désormais, toutes les demandes d'écriture sur la ROM ne feront rien. Cela permet également d'économiser de l'énergie car une seule puce est active au lieu des deux. Quant à la puce logique elle-même, nous avons encore deux onduleurs inutilisés à l'intérieur. On s'y habituera plus tard, mais on y arrivera quand on y sera.

Étape 3: LED d'état du système

Avant de commencer ce projet, j'essayais de m'interfacer avec un certain circuit intégré, mais j'avais des problèmes avec. Incertain de ce qui se passait, j'ai utilisé une LED à montage sur panneau pour sonder (un de ces ensembles qui a une résistance intégrée). Faire cela m'a donné une idée de nostalgie qui est encore utilisée aujourd'hui: les LED d'état utilisées pour indiquer si la mémoire était en cours de lecture ou d'écriture. Il devait être utilisé en conjonction avec la LED d'entrée que j'avais déjà. La LED d'entrée a été connectée au générateur de signal /WAIT pour nous indiquer que le système est, eh bien, en attente d'entrée (je vais y arriver, ne vous inquiétez pas). J'ai envisagé d'ajouter une LED pour indiquer une écriture d'E/S, mais j'ai pensé que les LED de sortie modifiées en seraient déjà un excellent indicateur. En y réfléchissant, je peux encore l'ajouter. Néanmoins, je trouve utile de savoir si la mémoire est en cours de lecture ou d'écriture. Eh bien, c'est utile pour le débogage du programme, de toute façon. En fait, je l'ai beaucoup utilisé en tant que tel pour essayer de faire fonctionner mon programme: « pourquoi écrit-il en mémoire ? Ce n'est pas encore censé faire ça !"

m

Pour contrôler ces LED, j'ai utilisé le quad NOR gate. J'ai utilisé toutes les portes. Seuls deux ont été utilisés pour générer les signaux d'état, mais la puce n'a pas les capacités d'alimentation pour réellement piloter les LED. Ils sont capables de couler autant de puissance, j'ai donc utilisé les deux autres portes NOR comme onduleurs et connecté les LED en tant que telles. Parce qu'une LED est utilisée pour indiquer les lectures et l'autre pour les écritures, et qu'une demande de lecture et d'écriture ne se produira pas en même temps, j'ai pu m'en tirer en utilisant une seule résistance pour les deux LED. Quant aux signaux que je devais décoder, c'était aussi assez facile. Je voulais que toutes les demandes de lecture de mémoire soient indiquées, donc la première porte NOR avait /MREQ et /RD sur ses entrées. Le statut d'écriture était un peu plus délicat, mais tout aussi facile. J'ai toujours utilisé /MREQ comme une entrée, mais utiliser /WR comme l'autre entraînerait une nuance mineure que je voulais éviter. Il aurait indiqué TOUTES les demandes d'écriture. Je ne voulais que ceux qui sont passés par là. Alors comment ferais-je ? Eh bien, rappelez-vous comment j'ai configuré le système pour que seule la RAM puisse être écrite ? J'ai utilisé les RAM /CE comme autre entrée de la porte NOR. Cela signifie que la LED ne s'allumera que lorsque la RAM est sélectionnée et qu'une demande d'écriture est en cours. En termes de couleur de LED, j'ai choisi l'orange comme indicateur de lecture (mais je n'ai trouvé que des jaunes) et le rouge comme indicateur d'écriture.

Étape 4: entrée et sortie

À l'étape précédente, vous avez peut-être remarqué que j'ai déjà ajouté certains des autres composants à la carte. Je réservais l'espace pour ne pas placer accidentellement des fils là où je voulais un composant (je devrais donc trouver un nouvel emplacement pour ledit composant). Vous avez peut-être également remarqué que j'ai laissé les commutateurs d'entrée en place et que je les ai câblés au rail d'alimentation. J'ai décidé que l'emplacement d'origine était l'endroit parfait et j'ai décidé de placer les LED de sortie à proximité (ci-dessus). À droite de l'affichage à barres se trouve le loquet d'entrée. Au-dessus se trouve le loquet de sortie et à gauche se trouve le pilote de LED. J'ai commencé par connecter l'écran au pilote car c'était le plus simple à faire. Ensuite, j'ai connecté les commutateurs au côté entrée du loquet d'entrée. Ensuite, j'ai connecté le côté sortie du loquet de sortie au pilote de LED. Cela peut sembler un ordre délicat pour les faire câbler, mais c'était pour une raison. L'entrée de la bascule de sortie devait être connectée au bus de données ainsi que la sortie de la bascule d'entrée. L'idée était de connecter les sorties du verrou d'entrée aux entrées du verrou de sortie, ce que j'ai fait. Ensuite, tout ce que j'avais à faire était de connecter ce désordre au bus de données. Peu importait où ces connexions allaient physiquement, car elles seraient toutes connectées électriquement. L'ordinateur est maintenant presque terminé.

Étape 5: Réinitialiser et terminer l'entrée et la sortie

Désolé, pas de photos pour cette étape. Reportez-vous à l'étape précédente pour les photos.

m

Vous avez peut-être remarqué dans la dernière photo de l'étape précédente, j'avais un bouton vert et une autre puce logique installée. La puce est la porte OU. Deux portes sont utilisées pour générer le signal /WAIT. Eh bien, on génère le signal par OU-ing /IORQ et /RD à partir du processeur. La sortie est introduite dans la deuxième porte, où elle est à nouveau OR à un bouton-poussoir. Le bouton amène l'entrée de la porte à un niveau élevé, amenant ainsi la sortie à un niveau élevé. Cette sortie est envoyée à la broche /WAIT du processeur. Lorsqu'elle n'est pas enfoncée, une résistance maintient l'entrée à un niveau bas. J'ai initialement utilisé une résistance de 10K, mais le LS32 mettait en fait une tension sur l'entrée. La résistance ne l'a pas laissé tomber assez bas et j'ai dû la remplacer par un 1K. Quoi qu'il en soit, l'idée est que lorsqu'une demande de lecture d'E/S est effectuée, les première et deuxième portes OU indiquent au processeur d'attendre. Une fois que vous avez réglé les commutateurs d'entrée sur ce que vous voulez, vous appuyez sur le bouton et le processeur sort de la condition d'attente. La LED verte "d'entrée", comme je l'ai appelée dans une étape précédente, est câblée de sorte que lorsque la broche /WAIT devient faible, elle s'allume.

m

Mais nous n'avons pas encore fini. La bascule d'entrée a besoin d'un signal pour lui faire savoir quand l'entrée de données est valide et doit être envoyée à la CPU. Cette broche d'horloge est active haut. Avant, on le connectait juste au bouton. C'est toujours une option valable, mais cette fois j'ai choisi de la mettre sur la même sortie que la deuxième porte OU. Ce circuit intégré a également une broche /OE qui doit être pilotée. S'il devait être maintenu haut, il n'insérerait jamais de données dans le bus. S'il était maintenu bas, il conduirait toujours le bus. Pour résoudre ce problème, j'ai simplement utilisé une troisième porte OU. Les entrées sont /IORQ et /RD et la sortie va directement au /OE du verrou.

m

Le verrou de sortie a également besoin de la broche d'horloge pour être entraînée. Encore une fois, il est actif haut. Dans mon schéma, j'ai dessiné la quatrième porte OU entraînant directement la broche en utilisant /IORQ et /WR. Cela signifiait que la broche d'horloge serait maintenue haute jusqu'à ce qu'une demande d'écriture soit faite, puis elle deviendrait basse puis haute à nouveau. Cela aurait probablement été bien car le bus de données aurait toujours des données valides immédiatement après la tentative d'écriture, mais d'un point de vue technique, c'était une conception erronée. Je n'ai remarqué cette erreur qu'après avoir pris les photos finales, mais j'ai déchiré cette connexion, puis j'ai alimenté la sortie de la porte OU dans l'un des inverseurs inutilisés de la logique de contrôle de la mémoire, puis j'ai connecté sa sortie à la broche d'horloge. J'ai également corrigé le schéma et trouvé une autre erreur que j'avais commise. Je l'ai corrigé aussi.

m

Avec tout cela enfin fait, j'avais une très petite quantité de travail à faire: le circuit de réinitialisation. J'ai ajouté un bouton à la carte et utilisé une résistance de 10K pour maintenir un côté haut. L'autre côté va directement au sol. Le côté élevé est la sortie /RESET, qui est allée à chaque puce avec une broche /RESET (le CPU et le verrou de sortie). Pour effectuer une réinitialisation à la mise sous tension, j'ai ajouté un condensateur à la sortie /RESET. L'idée est que la résistance de grande valeur entraînerait une charge lente du condensateur relativement important et maintiendrait les broches /RESET à un niveau bas pendant un certain nombre de cycles d'horloge (le processeur a besoin de quatre cycles d'horloge). Vous pouvez probablement déjà deviner quel est le côté négatif de ce circuit. C'est le même point négatif que la version précédente car c'est le même circuit. Lorsque le bouton est enfoncé, le condensateur est essentiellement court-circuité par le bouton. C'est mauvais pour le capuchon et le bouton, donc si vous voulez rendre votre construction un peu plus permanente, vous voudrez peut-être la reconcevoir. Je pensais à une autre minuterie 555 configurée en mode monostable. Mais avec cela, le circuit informatique est maintenant terminé. Yay. Maintenant, il doit être programmé.

Étape 6: Programmation

La programmation de cette chose était un cauchemar. J'ai construit un programmeur Arduino EEPROM. Cela n'a pas fonctionné. J'en ai construit un autre basé sur la conception et le codage de quelqu'un d'autre. N'a toujours pas fonctionné. Je suis revenu à la méthode éprouvée de définition manuelle des adresses et des octets de données. D'une certaine manière, j'ai tout gâché. J'ai réessayé et je me suis toujours trompé. J'y suis retourné encore une fois et j'ai découvert qu'il était décalé d'un seul octet, alors je l'ai corrigé et cela a finalement fonctionné, Dieu merci.

m

Quant au programme actuel, il semble qu'il soit super complexe et difficile à suivre, mais ce n'est pas le cas. C'est assez simple, en fait. La moitié copie des chiffres. L'autre moitié est partagée entre les mathématiques 16 bits, les sauts conditionnels et encore plus de nombres de copie. Alors laissez-moi passer en revue et vous dire comment cela fonctionne.

m

L'initialisation définit simplement certaines valeurs de registre à utiliser par le programme. La boucle du programme est un peu plus complexe, mais pas beaucoup. Tout d'abord, il accepte l'entrée dans le registre A sur le port 00. Ensuite, le registre E est écrit en mémoire. Sur les deux premières boucles, le registre E contient des données indésirables, nous essayons donc de les écrire dans les deux derniers octets de l'espace ROM car elles ne seront pas réellement écrites; le pointeur d'adresse (IY) est alors incrémenté. La valeur stockée dans D est ensuite déplacée dans E pour être écrite ensuite. A est ensuite chargé dans D et L et E est copié dans H. HL est l'endroit où la comparaison des valeurs a lieu via la soustraction et la vérification de ZF (drapeau zéro). La première valeur comparée est stockée dans les registres B et C. B et C sont traités comme un seul registre de 16 bits, BC. Si les valeurs sont les mêmes, alors le programme saute directement dans l'espace RAM, où le code utilisateur est supposé résider. Si le code dans BC ne correspond pas, alors HL est rechargé avec les valeurs initiales de D et E et est à nouveau comparé à la valeur dans SP de la même manière qu'il a été comparé à BC. S'il s'agit d'une correspondance, le résultat est le même, mais trois octets supplémentaires sont écrits en mémoire. Les octets sont un code qui fait revenir le CPU au tout début de son programme (une réinitialisation logicielle). Si la deuxième comparaison n'était pas une correspondance, cependant, le programme boucle là où il récupère une valeur de l'utilisateur.

m

LD SP, EDBFH; code exe (ajoute un saut)

m

LD IY, FFEH; pointeur de mémoire initial pour le stockage de code

m

LD BC, EDC3H; code exe (pas de boucle)

m

boucle; directive assembleur afin que nous n'ayons pas à savoir où en mémoire réside cette partie

m

EN A, (00H); obtenir les données du programme

m

LD (IY+00H), E; E contient le code à stocker

m

INC IY; passer à l'emplacement mémoire suivant

m

LD E, D; ld D dans E

m

LD D, A; ld A dans D

m

LD H, E; ld E dans H

m

LD L, D; ld D dans L

m

OU A; réinitialiser le drapeau de transport

m

SBC HL, C.-B.; renvoie 0 si le code exe 2 a été saisi

m

JP Z, 1000H; si c'est le cas, passez au programme et exécutez-le

m

LD H, E; sinon, actualisez-les aux valeurs appropriées

m

LD L, D

m

OU A; première soustraction peut avoir défini un indicateur de retenue. Efface ça

m

SBC HL, SP; renvoie 0 si le code exe 1 a été saisi

m

JP NZ, boucle; sinon, répétez le processus (en commençant par obtenir une valeur)

m

LD (IY+00H), C3H; sinon, injecter un code de saut à la fin du programme utilisateur

m

LD (IY+01H), 00H; jump agit essentiellement comme une réinitialisation logicielle

m

LD (IY+02H), 00H; c'est une réinitialisation complète au cas où les registres seraient modifiés

m

JP 1000H; sauter et exécuter le programme utilisateur

Conseillé:

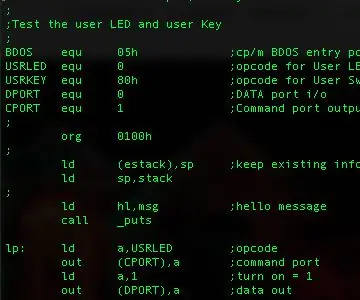

Z80-mbc2 Z80 Code Flash LED utilisateur : 3 étapes

Z80-mbc2 Z80 Code Flash User LED: Ceci est un exemple de programme utilisateur LED écrit en assembleur Z80 pour l'ordinateur z80-mbc2. J'ai fait cet exercice de test et de révision pour moi, c'est mon premier programme Z80 depuis plus de 35 ans

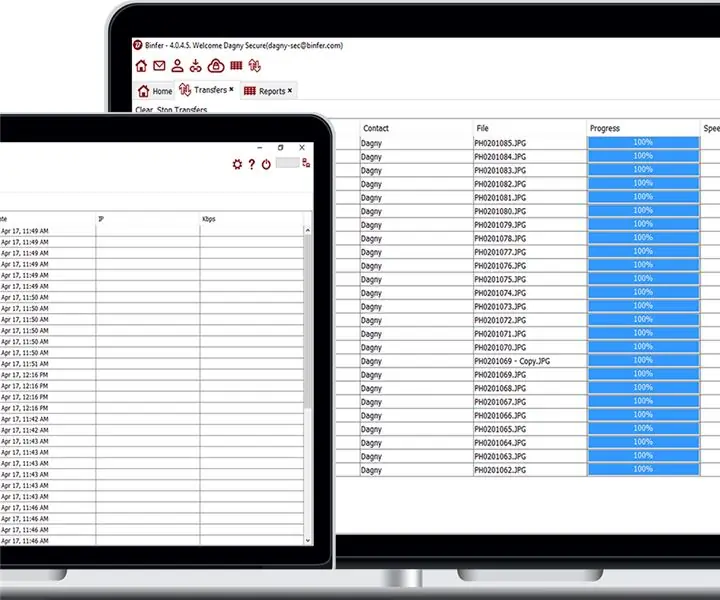

Comment envoyer des fichiers volumineux d'ordinateur à ordinateur : 6 étapes

Comment envoyer des fichiers volumineux d'un ordinateur à un autre : La taille des fichiers continue d'augmenter à mesure que la technologie progresse. Si vous êtes dans un métier créatif, comme la conception ou la modélisation, ou simplement un amateur, le transfert de fichiers volumineux peut être un problème. La plupart des services de messagerie limitent la taille maximale des pièces jointes à environ 25

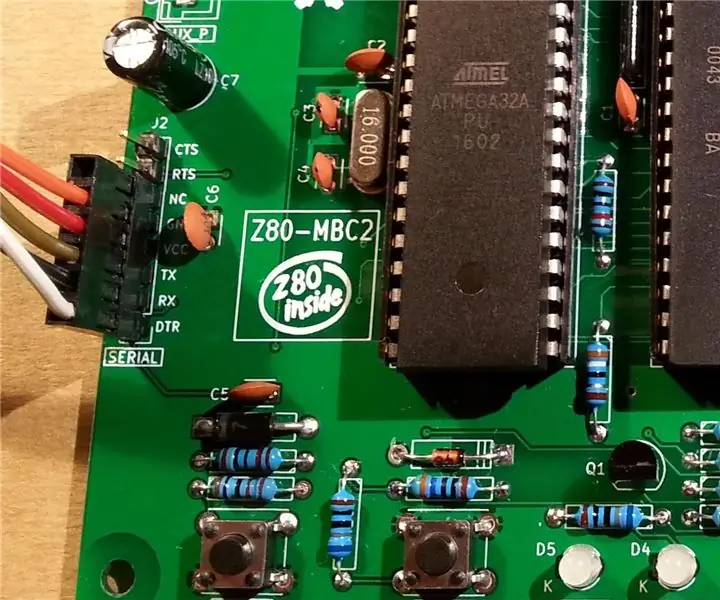

Un véritable ordinateur maison facile à construire : Z80-MBC2 ! : 9 étapes (avec photos)

Un vrai ordinateur fait maison facile à construire : Z80-MBC2 ! : Si vous êtes curieux de savoir comment un ordinateur fonctionne et interagit avec des "choses externes", il existe aujourd'hui de nombreuses cartes prêtes à jouer comme Arduino ou Raspberry et bien d'autres. Mais ces planches ont toutes la même "limite"… elles salut

Comment mettre à niveau un processeur d'ordinateur portable (et d'autres trucs sympas !) pour transformer un ordinateur portable SLOW/DEAD en un ordinateur portable RAPIDE ! : 4 ét

Comment mettre à niveau un processeur PORTABLE (et d'autres trucs sympas !) pour transformer un ordinateur portable SLOW/DEAD en un ordinateur portable RAPIDE ! très obsolète. . . L'écran LCD a été brisé et le disque dur principal s'est grippé, de sorte que l'ordinateur portable était essentiellement mort

Support d'ordinateur portable bon marché / Convertisseur d'ordinateur portable en ordinateur de bureau : 3 étapes

Support d'ordinateur portable bon marché / Convertisseur d'ordinateur portable en ordinateur de bureau : je me retrouve à utiliser mon ordinateur portable pendant de longues périodes. Cela devient inconfortable au bout d'un moment. Le clavier et l'écran doivent idéalement être séparés pour réduire la fatigue du cou lors d'une utilisation prolongée. Si vous êtes un utilisateur d'ordinateur portable à temps plein, je vous suggère de construire s