Table des matières:

- Étape 1: Création d'un module PWM - Fichier source

- Étape 2: Construire un module PWM - Configuration Vivado

- Étape 3: Construire un module PWM - Créer un fichier de projet

- Étape 4: Création d'un module PWM - Conception de blocs et configuration du fichier de contraintes (I)

- Étape 5: Création d'un module PWM - Conception de blocs et configuration du fichier de contraintes (II)

- Étape 6: Création d'un module PWM - Conception de blocs et configuration du fichier de contraintes (III)

- Étape 7: Création d'un module PWM - Conception de blocs et configuration du fichier de contraintes (IV)

- Étape 8: Création d'un module PWM - Conception de blocs et configuration du fichier de contraintes (V)

- Étape 9: Création d'un module PWM - Installation matérielle

- Étape 10: Construire un module PWM - Générer un flux de bits et lancer le SDK

- Étape 11: Construire un module PWM - Créer une nouvelle application dans Xilinx SDK

- Étape 12: Création d'un module PWM - Présentation de l'explorateur de projet (I)

- Étape 13: Création d'un module PWM - Présentation de l'explorateur de projet (II)

- Étape 14: Création d'un module PWM - Présentation de l'explorateur de projet (III)

- Étape 15: Création d'un module PWM - Fonction de clôture PWM (I)

- Étape 16: Création d'un module PWM - Fonction de clôture PWM (II)

- Étape 17: Création d'un module PWM - Fonction de synthèse PWM (III)

- Étape 18: Construire un module PWM - Faites-le fonctionner

- Étape 19: Traitement vidéo en streaming sur Digilent ZYBO avec OV7670

- Étape 20: Compléter le schéma fonctionnel

- Étape 21: Connectez l'OV7670 au ZYBO

- Étape 22: Créer une conception de bloc

- Étape 23: ajouter des fichiers VHDL pour le contrôle et la capture de la caméra OV7670

- Étape 24: Ajouter un fichier de contraintes

- Étape 25: Ajouter le référentiel IP pour l'IP HLS

- Étape 26: Ajouter des modules et IP

- Étape 27: Paramètres de configuration IP

- Étape 28: ajouter et configurer le bloc IP PS

- Étape 29: Partie 1. Construire un module PWM pour servomoteurs

- Étape 30: Connexions latérales d'entrée vidéo (aclk en surbrillance)

- Étape 31: Connexions à OV7670

- Étape 32: Connexions côté sortie vidéo

- Étape 33: Exécuter le blocage et l'automatisation des connexions

- Étape 34: Générer un wrapper HDL

- Étape 35: Générez Bitstream, exportez le matériel vers le SDK, lancez le SDK depuis Vivado

- Étape 36: SDK (pas de FreeRTOS)

- Étape 37: Implémentation de FreeRTOS

- Étape 38: Mode d'emploi

- Étape 39: Références et liens

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:09.

- Dernière modifié 2025-01-23 14:46.

Commencez à la première étape pour plus de détails sur la création d'un contrôleur PWM servo à 2 axes.

Commencez par le schéma fonctionnel massif (étape 19) pour le projet complet.

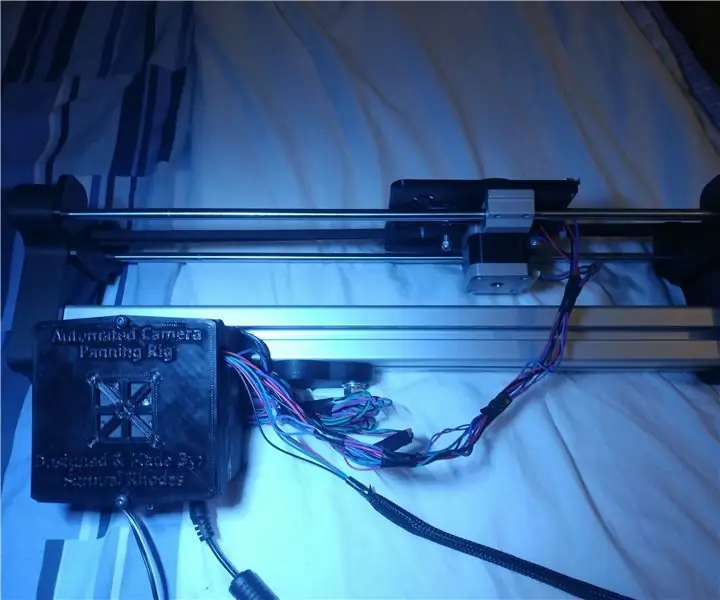

Caméra + configuration Pan/Tilt que nous avons utilisée:

Le PmodCON3 de Digilent a été utilisé pour connecter les servos.

Étape 1: Création d'un module PWM - Fichier source

Étape 2: Construire un module PWM - Configuration Vivado

Tout d'abord, téléchargez le site Web Vivado Design Suite de Xilinx. Installez toute la suite de conception, y compris le kit de développement logiciel Vivado (SDK). Ce projet utilise la version 2017.2.

En attendant, Digilent Adept 2 devrait également être installé en tant que pilote de carte Zybo.

Étape 3: Construire un module PWM - Créer un fichier de projet

Avant de créer un fichier de projet, vous devez vous assurer que vous avez déjà correctement installé le fichier Zybo comme le tutoriel ici:

Installation du fichier de carte Vivado version 2015.1 et versions ultérieures

Ouvrez Vivado 2017.2. Dans Quick Start, cliquez sur Créer un projet -> Suivant -> Nom du projet (nommez le nom de votre projet ici) -> Type de projet. Dans Type de projet, sélectionnez Projet RTL et cochez « Ne pas spécifier de sources pour le moment ». Ensuite, pour la pièce par défaut, sélectionnez « Boards » et « Zybo » comme nom d'affichage. Ensuite, cliquez sur Terminer pour démarrer le projet.

Étape 4: Création d'un module PWM - Conception de blocs et configuration du fichier de contraintes (I)

Sur Flow Navigator, cliquez sur ""Créer une conception de bloc", puis appuyez sur OK. cliquez sur le signe "+" pour ajouter les adresses IP nécessaires. Ajouter:

- Un système de traitement ZYNQ7 Deux minuteries AXI

- Minuterie deux AXI

Étape 5: Création d'un module PWM - Conception de blocs et configuration du fichier de contraintes (II)

Après avoir ajouté des adresses IP, exécutez l'automatisation des blocs et l'automatisation de la connexion. Une fois l'automatisation terminée, sur le bloc « axi_timer_0 », clic droit sur pwm0 -> Make External. Nommez la broche externe pwm0 comme pwm_Xaxis. Répétez également le processus ci-dessus sur le bloc "axi_timer_1" et nommez la broche externe pwm0 comme pwm_Zaxis.

Étape 6: Création d'un module PWM - Conception de blocs et configuration du fichier de contraintes (III)

Notez que chaque fois que nous terminons le Block Design dans Vivado, nous devons créer un wrapper HDL. Puisqu'il s'agira du module de niveau supérieur pour chaque projet.

Étape 7: Création d'un module PWM - Conception de blocs et configuration du fichier de contraintes (IV)

Maintenant, nous devons configurer notre fichier de contraintes pour affecter des broches connectées à notre diagramme. Fermez la fenêtre Block Design, Sur l'onglet Sources, "Ajouter des sources" -> Ajouter ou créer des contraintes -> ajoutez le Zybo-Master.xdc comme nos fichiers de contraintes.

Étape 8: Création d'un module PWM - Conception de blocs et configuration du fichier de contraintes (V)

Ouvrez le fichier de contraintes Zybo-Master.xdc à partir du dossier Constraints, décommentez les ports que nous voulons spécifier comme signaux de sortie et renommez « get_ports{XXXX} », qui XXXX désigne la broche externe nommée dans le schéma fonctionnel. Le paramétrage du fichier de contraintes est indiqué sur la figure.

Étape 9: Création d'un module PWM - Installation matérielle

Connectez les servomoteurs au Pmod CON3. TowerPro SG90 est le modèle de servomoteur que nous avons utilisé dans ce projet. Pour les fils du servomoteur, le fil orange représente le signal PWM, connecté à la broche SIG dans Pmod CON3. Le fil rouge Vcc est un fil d'alimentation connecté à la broche VS dans Pmod CON3. Enfin, le fil marron Gnd est un fil de terre connecté à la broche GND. Ensuite, insérez le Pmod CON3 dans la rangée supérieure du port JD de la carte Zybo.

Étape 10: Construire un module PWM - Générer un flux de bits et lancer le SDK

1. Dans l'onglet Navigateur de projet, exécutez Générer BitStream.

2. Exporter le matériel: Fichier > Exporter > Exporter le matériel -> Marquer sur « inclure le flux binaire » -> OK 3. Lancer le SDK: Fichier -> Lancer le SDK.

Étape 11: Construire un module PWM - Créer une nouvelle application dans Xilinx SDK

Créer une nouvelle application:

Fichier > Nouveau > Projet d'application -> Entrez le nom de votre projet -> Terminer

Sous Explorateur de projets, il doit y avoir trois dossiers.

Dans ce cas, « design_1_wrapper_hw_platform_0 » est le dossier précédemment exporté par Vivado. Axis_2_PWM_SDK_bsp est le dossier du package de support de carte. Et Axis_2_PWM_SDK est notre dossier de projet principal dans le SDK. Vous pouvez voir le fichier « helloworld.c » sous le dossier « src » de Axis_2_PWM_SDK, où « helloworld.c » est le fichier principal.

Étape 12: Création d'un module PWM - Présentation de l'explorateur de projet (I)

Vérifions quelques fichiers sous Project Explorer. Tout d'abord, dans le dossier "design_1_wrapper_hw_platform_0", ouvrez le "system.hdf". Ce fichier montre la carte d'adresses du processeur ps7_cortex9 et les blocs IP présents dans notre conception.

Étape 13: Création d'un module PWM - Présentation de l'explorateur de projet (II)

Ensuite, vérifiez les fichiers « include » et « libsrc » dans le dossier « Axis_2_PWM_SDK_bsp ». Les fichiers de bibliothèque nous permettent ici d'interagir avec les périphériques matériels sans « jouer » des registres.

Étape 14: Création d'un module PWM - Présentation de l'explorateur de projet (III)

Grâce à la documentation BSP, xtmrctr.h se trouve en tant que bibliothèque de contrôle de minuterie Xilinx liée à AXI Timer. En règle générale, nous pourrions trouver la fonction PWM souhaitée ici. Cependant, si vous lisez la documentation "tmrctr_v4_3", cela montre que le pilote ne prend actuellement pas en charge le fonctionnement PWM de l'appareil. En raison de la déficience de la fonction PWM, nous devons terminer notre fonction PWM à l'aide de xtmrctr.h et AXI Timer v2.0 LogiCORE IP Product Guide.

Étape 15: Création d'un module PWM - Fonction de clôture PWM (I)

De retour au fichier principal "helloworld.c", incluez les fichiers d'en-tête suivants:

Étape 16: Création d'un module PWM - Fonction de clôture PWM (II)

Définissez les adresses de base de deux AXI TImer via « xparameters.h ».

Étape 17: Création d'un module PWM - Fonction de synthèse PWM (III)

Créez la fonction PWM souhaitée.

Duty_val: convertit la valeur du degré en cycle de service. PWM_Freq_Duty: définissez la fréquence et le cycle de service souhaités pour générer le PWM. La période d'horloge doit également être attribuée.

PWM_START: attribuez l'adresse du registre PWM et commencez à générer PWM.

PWM_STOP: attribuez l'adresse du registre PWM et arrêtez de générer PWM.

Le reste du code de démonstration est affiché dans « helloworld.c » sous « Axis_2_PWM_SDK »

Étape 18: Construire un module PWM - Faites-le fonctionner

1. Programmer le FPGA via SDK

- Connectez la carte Zybo via le port USB au PC.

- Outils Xilinx -> Programmer FPGA

2. Exécutez le programme

Cliquez sur l'icône "Exécuter" et déroulez le menu -> Exécuter en tant que -> Lancer sur le matériel

3. Terminal SDK

- Ouvrez le terminal SDK -> Connectez-vous au port série -> OK

- Exécutez le programme. Si le code de démonstration s'exécute avec succès, vous devriez voir « Initialisation effectuée ! » sur le terminal SDK.

Étape 19: Traitement vidéo en streaming sur Digilent ZYBO avec OV7670

Fichier d'archive complet joint.

Étape 20: Compléter le schéma fonctionnel

Cela montre le schéma complet de toutes les connexions et blocs IP dans le projet

Étape 21: Connectez l'OV7670 au ZYBO

Créez une connexion pour câbler le module ov7670 aux Pmods ZYBO

Les données Pmod sont Pmod D

Le contrôle Pmod est Pmod C

De plus, connectez le PmodCON3 et les servos comme spécifié dans la première moitié de ce tutoriel

Étape 22: Créer une conception de bloc

Dans Flow Navigator, cliquez sur "Créer une conception de bloc", puis appuyez sur OK.

Étape 23: ajouter des fichiers VHDL pour le contrôle et la capture de la caméra OV7670

Ajouter les fichiers VHDL attachés à cette étape au projet

Étape 24: Ajouter un fichier de contraintes

Ajoutez le fichier de contraintes joint à votre projet.

Étape 25: Ajouter le référentiel IP pour l'IP HLS

Prenez le fichier Zip joint et décompressez-le dans un nouveau dossier nommé de la même manière dans un nouveau répertoire (dossier) appelé "HLS_repo".

Ajoutez un référentiel IP à votre projet en accédant au catalogue IP et faites un clic droit en sélectionnant "Ajouter un référentiel…"

Accédez à votre répertoire "HLS_repo" et sélectionnez-le.

Facultatif: créez vous-même le bloc de traitement vidéo HLS !

Étape 26: Ajouter des modules et IP

Ajoutez les modules ov7670_axi_stream_capture, debounce et ov7670_controller au diagramme en cliquant avec le bouton droit sur l'arrière-plan et en sélectionnant « Ajouter un module… »

De même, ajoutez les IP:

- HLS_Video_Track

- Écriture dans le tampon de trame vidéo

- Lecture du tampon de trame vidéo

- Contrôleur de synchronisation vidéo

- AXI4-Stream vers sortie vidéo

- 3 de "tranche"

- Constant

- 2 de la minuterie AXI

Étape 27: Paramètres de configuration IP

Comme le montrent les images

Étape 28: ajouter et configurer le bloc IP PS

Ajouter le système de traitement ZYNQ7 au schéma fonctionnel

modifier la configuration:

-

Configuration PS-PL

-

HP

- Activer S HP 0

- Activer S HP 1

-

-

Configuration de l'horloge

-

Horloges en tissu PL

- FCLK_0 à 100MHz

- FCLK_1 à 25MHz (OutputClock)

- FLCK_2 à 35MHz (<=50MHz) (CameraClock)

-

Étape 29: Partie 1. Construire un module PWM pour servomoteurs

Sortez axi_timer_0 pwm0 vers le nouveau port de sortie pwm_Xaxis

Sortez axi_timer_1 pwm0 sur le nouveau port de sortie pwm_Zaxis

Étape 30: Connexions latérales d'entrée vidéo (aclk en surbrillance)

Connectez correctement les blocs IP côté entrée vidéo

(* ces connexions doivent être créées en sélectionnant les bonnes options lors de l'automatisation de la connexion) "aclk" de axi_stream_capture va à:

- ap_clk sur l'écriture du tampon de trame vidéo

- ap_clk sur le bloc de traitement de flux vidéo HLS

- *aclk sur AXI smartconnect IP depuis le Video Frame Buffer Write vers le S_AXI_HP0

- *aclk correspondant aux canaux de l'AXI Interconnect IP pour les canaux S_AXI du bloc de traitement vidéo HLS et le tampon de trame vidéo écrivez S_AXI_HP0_ACLK sur le bloc PS

Le signal du flux vidéo est simplement connecté en série du bloc de capture à l'interface mémoire Zynq.

- La vidéo passe du bloc de capture au bloc de traitement HLS.

- La vidéo traitée du bloc HLS va au bloc d'écriture du tampon de trame.

- *Le bloc d'écriture du tampon de trame se connecte à l'interface HP0 sur le bloc Zynq PS.

- Le signal m_axis_tuser de la sortie du bloc de capture est câblé manuellement à la fois au signal d'entrée video_in_TUSER sur le bloc de traitement HLS et au signal ap_start sur le même bloc.

Le signal TUSER (tuser) est utilisé par le protocole de flux vidéo AXI pour indiquer le début d'une image de la vidéo. AP_Start indique au bloc HLS de commencer le traitement. Nous utilisons donc tuser pour déclencher le bloc HLS afin de traiter chaque image comme elle Lorsque vous connectez un seul signal d'un bus et le séparez de cette manière, il est également nécessaire de le connecter au point de terminaison normal du reste du bus. Vivado suppose que si vous connectez le signal manuellement, vous souhaitez déconnecter ce à quoi il se connecterait normalement.

Paramètres de configuration des blocs IP:

Ecriture du tampon d'images vidéo:

Formats vidéo: RGB8

1 échantillon par horloge Colonnes max: 1280 (>=640) Lignes max: 960 (>=480) Largeur de données max: 8

Étape 31: Connexions à OV7670

Sur le bloc ov7670_axi_stream_capture

- Rendre toutes les entrées externes (clic droit sur une épingle et sélectionner dans le menu, ou clic gauche->ctrl+T)

- Laissez les noms tels qu'ils sont

Sur le bloc ov7670_controller

- Rendre toutes les sorties de bloc externes

- Renommez le port config_finished en led0

- connectez clk à la CameraClock (<=50MHz) (FCLK_2)

Sur le bloc anti-rebond

- connectez l'entrée button1 à un port d'entrée externe appelé btn0

- connectez le out1 à la ligne de renvoi sur le bloc IP ov7670_controller

- connectez l'entrée button2 à un port d'entrée externe appelé btn3

- connectez le out2n à l'entrée ext_reset_in sur l'IP de réinitialisation du système de processeur pour le domaine d'horloge de capture vidéo. (*Cela peut être nécessaire après la génération de cette IP*)

- connectez clk à la CameraClock (<=50MHz) (FCLK_2)

Étape 32: Connexions côté sortie vidéo

Connexions pour blocs Video Timing Controller (VTC), AXI4-Stream to Video Out et slices

- Utilisez une horloge à 25 MHz (FCLK_1) pour vid_io_out_clk et VTC clk

- Utilisez une horloge de 100 MHz (FCLK_0) pour aclk sur AXI4-Stream vers la sortie vidéo

- vtiming_out à vtiming_in

- Lecture du tampon de trame vidéo m_axis_video va vers AXI4-Stream vers la sortie vidéo video_in

- vtg_ce va à gen_clken

- Liez VTC clken, aclken, vid_io_out_ce à Constant dout[0:0]

- Sortez vid_hsync et vid_vsync vers les ports de sortie externes vga_hs et vga_vs, respectivement. (pas sur la photo)

Tranches:

-

Les tranches doivent être configurées comme indiqué sur les images ci-jointes

- renommer les blocs en slice_red, slice_green et slice_blue

- configurer les plages de tranches comme indiqué dans les images par le nom du bloc

- connectez chaque sortie de tranche à une sortie de port externe comme indiqué dans l'image.

- vid_data[23:0] se connecte aux entrées pour chaque tranche (Din[23:0])

Étape 33: Exécuter le blocage et l'automatisation des connexions

Exécutez Block Automation pour connecter les éléments du bloc ZYNQ7 PS. Comme le montre l'image.

Exécutez l'automatisation de la connexion pour créer toutes les IP d'interconnexion. Portez une attention particulière à toutes les options dans chaque image.

Sur le bloc anti-rebond, connectez out2n à l'entrée ext_reset_in de réinitialisation du système du processeur du domaine d'horloge de capture vidéo.

Étape 34: Générer un wrapper HDL

Générez le wrapper HDL pour votre conception de bloc.

Définissez-le comme module supérieur.

Étape 35: Générez Bitstream, exportez le matériel vers le SDK, lancez le SDK depuis Vivado

Assurez-vous d'inclure bitstream dans l'exportation.

La génération du flux binaire peut prendre un temps très long.

Puis lancez le SDK

Étape 36: SDK (pas de FreeRTOS)

Cette version fait tout sans utiliser FreeRTOS, condensant bien le code.

Créez un BSP autonome basé sur la conception matérielle. Les options par défaut devraient convenir. Assurez-vous que les sources BSP ont été générées.

Créez l'application comme indiqué dans l'image. (demande vide)

Supprimez le fichier principal généré automatiquement et importez les fichiers joints.

Étape 37: Implémentation de FreeRTOS

Cette version utilise FreeRTOS. Créez un BSP FreeRTOS901 basé sur la conception matérielle. Les options par défaut devraient convenir. Assurez-vous que les sources BSP ont été générées.

Créez l'application comme indiqué dans l'image. (demande vide)

Supprimez le fichier principal généré automatiquement et importez les fichiers joints.

Étape 38: Mode d'emploi

Ce projet est un peu délicat à mettre en place. Suivez les étapes dans l'ordre.

Assurez-vous que votre ZYBO ne charge rien lorsqu'il est allumé. Cela signifie que la LED Done ne doit pas s'allumer. Une façon de le faire est de définir le cavalier de la source de démarrage sur JTAG.

Ouvrez le projet (FreeRTOS ou non) que vous souhaitez programmer à partir du SDK

- Allumez votre ZYBO. La LED Done ne doit pas s'allumer.

- Programmez le FPGA avec le fichier bit. La LED Done doit s'allumer. Led0 ne doit pas s'allumer.

- Exécutez le code (n'oubliez pas de dépasser le point d'arrêt de démarrage si vous le faites).

À ce stade, vous devriez obtenir une sortie sur votre écran VGA.

Pour redémarrer (en cas de bug ou autre): appuyez rapidement sur le bouton PS-SRST ou éteignez puis rallumez le ZYBO. Continuez à partir de l'étape 2.

Si vous arrêtez le processeur avec le débogueur, la caméra restera en position au lieu de bouger. Le flux vidéo continuera de toute façon.

Étape 39: Références et liens

Guides de référence et documentation Xilinx:

- PG044 - AXI-Stream vers sortie vidéo

- PG278 - Lecture/écriture de tampon de trame vidéo

Autres liens:

- Le blog de Lauri - Entrée VDMA

- Le blog de Lauri - Sortie OV7670 vers VGA en utilisant BRAM

- Wiki Hamsterworks, par Mike Fields, la source originale du code OV7670

- Fiche technique montrant les spécifications de synchronisation de base

Conseillé:

Appareil photo panoramique entièrement automatisé : 14 étapes (avec photos)

Appareil photo panoramique entièrement automatisé : introductionSalut à tous, voici mon appareil photo panoramique automatique ! panoramique ? Eh bien, arrêtez-vous ici

Mécanisme de panoramique et d'inclinaison pour les laps de temps DSLR : 7 étapes (avec photos)

Mécanisme Pan and Tilt pour DSLR Time Lapse : j'avais quelques moteurs pas à pas qui traînaient et je voulais vraiment les utiliser pour faire quelque chose de cool. J'ai décidé de créer un système Pan and Tilt pour mon appareil photo reflex numérique afin de pouvoir créer des intervalles de temps intéressants. Articles dont vous aurez besoin : 2x moteurs pas à pas -htt

Stabilisateur d'appareil photo pour ENV2 ou autres téléphones avec appareil photo : 6 étapes

Stabilisateur d'appareil photo pour ENV2 ou autres téléphones avec appareil photo : vous avez toujours voulu faire une vidéo mais vous n'avez qu'un téléphone avec appareil photo ? Avez-vous déjà fait une vidéo avec un téléphone appareil photo mais vous ne pouvez pas le maintenir immobile ? Eh bien, c'est l'instructable pour vous

Appareil photo pour des images accélérées en toute simplicité. : 22 étapes (avec images)

Appareil photo pour Time Lapse Pictures Made Easy. : Je vérifiais l'un des autres Instructables sur la création de films en accéléré. Il a assez bien couvert la partie film. Il a parlé du logiciel gratuit que vous pouvez télécharger pour faire des films. Je me suis dit, je pense que je vais voir si je peux m

Prenez d'incroyables photos macro avec n'importe quel appareil photo Appareil photo Surtout un IPhone : 6 étapes

Prenez d'incroyables photos macro avec n'importe quel appareil photo. !? Fondamentalement, il s'agit d'un addon d'augmentation pour n'importe quel appareil photo de téléphone portable pour agrandir l'objectif de votre appareil photo existant pour prendre