Table des matières:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:06.

- Dernière modifié 2025-01-23 14:45.

Connectez votre carte de développement Mojo à des entrées externes avec ce shield.

Qu'est-ce que la carte de développement Mojo ?

La carte de développement Mojo est une carte de développement basée sur le FPGA Xilinx spartan 3. La planche est faite par Alchitry. Les FPGA sont très utiles lorsque plusieurs processus doivent être exécutés simultanément.

De quoi aurez-vous besoin ?

Fournitures

Carte de développement Mojo

fichier Gerber

8 résistances de 15k ohms (en option*)

4 résistances de 470 ohms

4 résistances de 560 ohms

4 écrans CC à sept segments

4 LED de 3 mm

4 x commutateurs tactiles SPDT

1 commutateur DIP à 4 positions pour montage en surface

2 x 25 par 2 ou 4 x 25 en-têtes

1x tête de boîte 2 par 5 broches

Fer à souder

Souder

Flux

*(si ces résistances sont omises, le pullup/pulldown interne doit être activé pour les broches concernées)

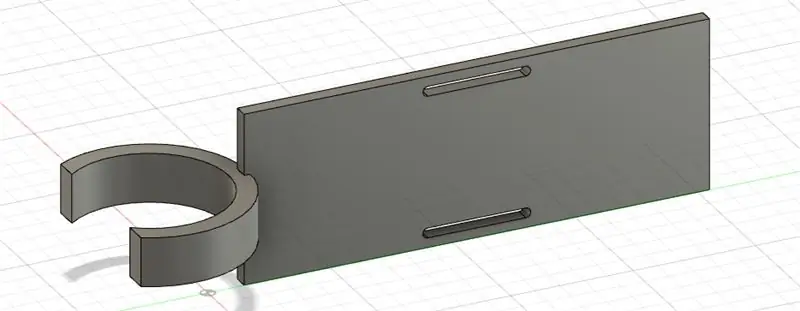

Étape 1: Téléchargez Gerber sur le fabricant de circuits imprimés de votre choix

Pour mes cartes, j'ai commandé chez JLC PCB.

Le seul changement que j'ai fait était la couleur que je voulais faire correspondre au noir du Mojo.

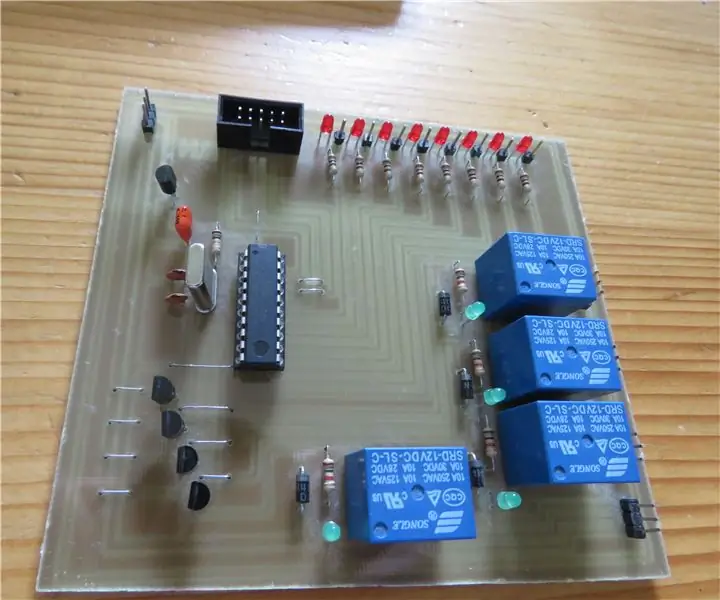

Étape 2: Assemblage de la carte

Lors de la soudure, je trouve toujours utile de souder d'abord les pièces les plus basses, donc commencer par les résistances est une bonne idée.

R5, R6, R7, R8, R9, R10, R11 et R12 sont des résistances de 15 k ohms utilisées pour abaisser les commutateurs (si vous utilisez un pullup/pulldown interne, ignorez-le).

R1, R2, R3, R4 sont des résistances de 560 ohms qui sont chargées de limiter le courant à travers l'affichage à 7 segments.

R13, R14, R15, R16 sont des résistances de 470 ohms qui sont chargées de limiter le courant à travers les 4 LED.

Ensuite, soudez le commutateur DIP, les commutateurs tactiles, les LED, les écrans à sept segments et le connecteur d'en-tête de boîte dans cet ordre.

Placez maintenant le 25 par 2 (ou 2 25 par 1) dans le mojo pour aligner les broches. Alignez le blindage avec les broches et soudez-le en place.

Étape 3: Configuration du logiciel

Pour les logiciels, se référer au site Web d'Alchitry vous indiquera ce dont vous avez besoin pour commencer et installer le Xilinx ISE. Cependant, changer le fichier.ucf pour qu'il sache quelles broches sont connectées à ce qui est important pour faire fonctionner votre programme.

Voici le fichier.ucf que j'utilise avec le shield:

CONFIG VCCAUX=3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PÉRIODE "clk" 50 MHz HAUT 50 %; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q[0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q[1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q[2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q[3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S[0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S[1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S[2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S[3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb[1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb[2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb[3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb[4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega[0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb[0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc[0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd[0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege[0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf[0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg[0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp[0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega[1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb[1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc[1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd[1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege[1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf[1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg[1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp[1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega[2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb[2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc[2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd[2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege[2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf[2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg[2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp[2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega[3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb[3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc[3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd[3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege[3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf[3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg[3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp[3]" LOC = P121 | IOSTANDARD = LVTTL;

N'oubliez pas que si vous n'avez pas installé les résistances pulldown pour éditer les broches dans le.ucf avec

| TIRER VERS LE BAS; o

| REMONTER;

Si vous souhaitez utiliser le bloc pour quoi que ce soit, les connexions sont les suivantes. Gauche étant le numéro de broche de bloc et droite étant le numéro de broche mojo que vous devez attribuer dans votre.ucf:

broche 1 = 29

broche 2 = 51

broche 3 = 32

broche 4 = 41

broche 5 = 34

broche 6 = 35

broche 7 = 40

broche 8 = 33

broche 9 = GND

broche 10 = +V

Conseillé:

Développement de la carte Drivemall : 5 étapes

Développement de la carte Drivemall : Dans ce tutoriel, nous verrons les étapes de base pour créer une carte Arduino personnalisée. Les logiciels utilisés sont KiCad pour la conception de la carte et l'IDE Arduino pour la création et le chargement du firmware de la carte

Carte de développement DIY ESP32 - ESPer : 5 étapes (avec photos)

Carte de développement DIY ESP32 - ESPer : J'avais récemment lu beaucoup d'IoT (Internet des objets) et croyez-moi, j'avais hâte de tester l'un de ces merveilleux appareils, avec la possibilité de se connecter à Internet, moi-même et mettre la main sur le travail. Heureusement, l'opportunité d'un

Créez votre propre carte de développement avec microcontrôleur : 3 étapes (avec photos)

Faites votre propre carte de développement avec microcontrôleur : avez-vous déjà voulu faire votre propre carte de développement avec microcontrôleur et vous ne saviez pas comment. et la programmation. Si vous avez une quête

Jouer au jeu Flappy Bird avec la carte de développement M5stick C basée sur M5stack Esp32 : 5 étapes

Jouer au jeu Flappy Bird avec la carte de développement M5stick C basée sur M5stack Esp32 : Salut les gars, aujourd'hui, nous allons apprendre à télécharger le code du jeu Flappy Bird sur la carte de développement m5stick c fournie par m5stack. Pour ce petit projet, vous aurez besoin de deux choses : m5stick-c conseil de développement : https://www.utsource.net/itm/p/8663561.h

Carte de développement JALPIC One : 5 étapes (avec photos)

Carte de développement JALPIC One : Si vous suivez mes projets Instructables, vous savez que je suis un grand fan du langage de programmation JAL en combinaison avec le microcontrôleur PIC. JAL est un langage de programmation de type Pascal développé pour les microcontrôleurs PIC 8 bits de Microchip. Mo