Table des matières:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:08.

- Dernière modifié 2025-01-23 14:46.

Je sais ce que vous pensez: « Hein ? Il y a beaucoup d'Instructables sur la façon d'utiliser des microcontrôleurs pour mesurer la fréquence du signal. Bâillement. Mais attendez, il y a une nouveauté dans celui-ci: je décris une méthode de mesure de fréquences bien supérieures à ce qu'un microcontrôleur (MCU) peut supporter et le rapport cyclique du signal - le tout en même temps !

La plage de fréquences de l'appareil s'étend de ~43 Hz à ~450 kHz, tandis que le cycle de service varie de 1 % à 99 %.

Permettez-moi d'expliquer la partie "peut supporter": un MCU mesure la période d'un signal d'onde carrée, T, en suivant le temps entre deux événements de transition ultérieurs. Par exemple, une tension faible à élevée saute sur l'une de ses broches d'E/S. Il le fait en comptant le nombre d'impulsions de sa propre horloge interne. Naïvement, la limite supérieure des fréquences mesurées devrait obéir au théorème d'échantillonnage de Nyqvist-Shannon; c'est-à-dire qu'elle serait à peu près égale à la moitié de la fréquence d'horloge des MCU. En réalité, la limite est beaucoup, beaucoup plus basse, car le MCU doit exécuter du code pour gérer les interruptions, enregistrer les variables, effectuer des opérations arithmétiques, afficher les résultats, etc. Dans mes expériences avec un MCU à 48 MHz, le nombre minimal de cycles d'horloge entre les transitions mesurables était environ 106. Par conséquent, la limite supérieure de la gamme de fréquences mesurables dans ce cas serait de 48 000 / 212 / 2 = 226,4 kHz.

Alors que le MCU mesure la période du signal, il peut également déterminer sa largeur d'impulsion, P: le temps pendant lequel la tension du signal reste élevée. En d'autres termes, le temps entre les transitions bas-à-haut et haut-bas. Le rapport cyclique du signal est alors défini comme le pourcentage suivant:

Devoir = 100% * P/T

Tout comme dans le cas de la fréquence, il existe une limite pratique sur la largeur d'impulsion. En utilisant l'exemple ci-dessus, 106 cycles d'horloge limiteraient la largeur d'impulsion à pas moins de 2,21 microsecondes. Soit pas moins de 50 % à 226,4 kHz.

L'un des moyens d'augmenter la limite de fréquence supérieure des signaux d'onde carrée est l'application de diviseurs numériques qui utilisent des bascules. Diviser la fréquence d'entrée par n étendrait la plage supérieure mesurable n fois. C'est une excellente nouvelle, les diviseurs numériques ont un défaut fondamental: le signal divisé perd les informations sur la largeur d'impulsion (et le rapport cyclique) ! En raison de la façon dont les diviseurs fonctionnent, leur sortie a toujours un facteur de marche de 50 %. Dommage…

Dans les pages suivantes, cependant, je montrerai comment diviser numériquement la fréquence et préserver la largeur d'impulsion d'origine me permettant de mesurer des signaux bien au-delà des limites imposées par le comptage direct.

Étape 1: Division de fréquence numérique

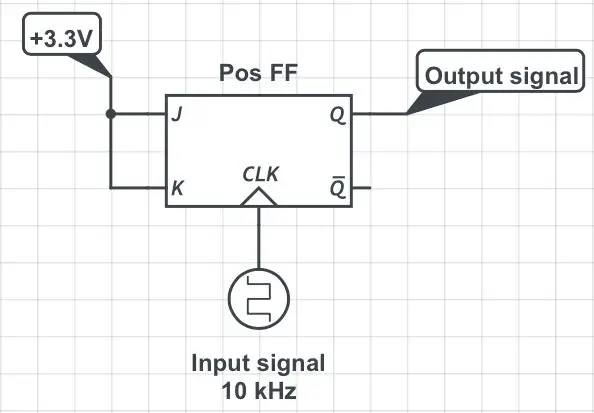

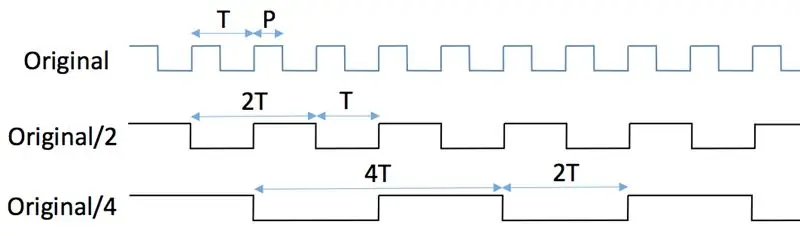

Les diviseurs de fréquence numériques traditionnels utilisent des bascules; ce tutoriel explique bien les principes de construction de diviseurs à l'aide de bascules JK standard. Cela résout le problème des fréquences d'entrée trop élevées pour le MCU, mais présente un inconvénient majeur: le signal divisé a un cycle de service de 50 % quel que soit le service du signal d'entrée ! Pour voir pourquoi c'est le cas, regardez les deux premiers chiffres. Le signal d'origine avec une période T et une largeur d'impulsion P est introduit dans la broche d'horloge d'une bascule JK tandis que ses broches J et K sont maintenues hautes à tout moment (première figure). Une logique de 3,3 V est supposée tout au long. Supposons que la bascule est déclenchée par le front positif (c'est-à-dire montant) de l'horloge. Dans ces conditions, des changements d'état de la broche de sortie ("flips" et "flops" individuels) se produisent chaque fois que la broche d'horloge passe de bas en haut. La transition de haut en bas de l'horloge (c'est-à-dire le front négatif) est complètement ignorée. Voir la deuxième figure. La broche de sortie, Q, émet un signal dont la période est deux fois plus longue que la période d'origine, c'est-à-dire que sa fréquence est réduite de moitié. La largeur d'impulsion de la sortie est toujours égale à T. Par conséquent, la largeur d'impulsion d'origine, P, est perdue.

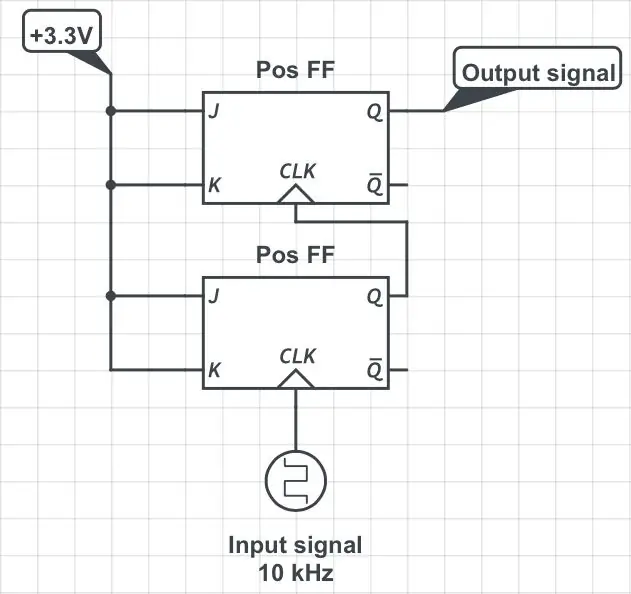

L'ajout d'une autre bascule JK dans une configuration illustrée dans la troisième figure divise la fréquence d'origine par 4. L'ajout de bascules supplémentaires de la même manière séquentielle divise la fréquence par les puissances suivantes de 2: 8, 16, 32, etc.

Problème: comment diviser la fréquence d'une onde carrée tout en préservant sa largeur d'impulsion ?

L'idée est d'ajouter correctement une bascule JK déclenchée par un front négatif au mix. Appelons-le "Neg FF"; voir quatrième figure. Ici, "correctement" signifie que les broches J et K de la nouvelle bascule sont liées aux broches de sortie Q et Qbar, respectivement, du diviseur par 4 ("Pos FF") illustré dans la figure précédente. (Ici, "bar" est la barre horizontale au-dessus du symbole Q indiquant une négation logique.) Pour voir ce que cela permet, jetez un œil à la table des fonctions du "Neg FF" dans la cinquième figure: broches de sortie de Neg, Q et Qbar, reflète l'état de ses broches d'entrée, J et K, respectivement. Ce qui signifie qu'ils reflètent l'état du Pos' Q et Qbar. Mais, l'action de bascule de Neg doit attendre le front négatif du signal d'origine, qui arrive au temps P après le front positif. Ah !

Les formes d'onde résultantes sont illustrées dans la sixième figure. "Pos Q" produit un signal à la fréquence 1/4, "Pos Qbar" est inverse, "Neg Q" suit "Pos Q" décalé de la largeur d'impulsion P et "Neg Qbar" est son inverse. Vous pouvez vérifier que le ET logique de "Pos Qbar" et "Neg Q" produit un train d'impulsions caractérisé par la largeur d'impulsion d'origine P et 1/4 de la fréquence. Bingo !

Au début, j'ai utilisé exactement ce signal de sortie pour alimenter le MCU. Cependant, cela s'est avéré problématique pour des largeurs d'impulsion très courtes en raison de la limitation de 106 cycles du MCU mentionnée dans l'introduction. J'ai résolu ce petit problème en choisissant une autre sortie: "Pos Qbar" ET "Neg Qbar" à la place. Un coup d'œil aux formes d'onde devrait vous convaincre que la largeur d'impulsion de cette forme d'onde particulière, P', varie entre T et 2T au lieu de (0, T) pour P. Le P peut être facilement récupéré à partir de P' en:

P = 2T - P'

Étape 2: Matériel recommandé

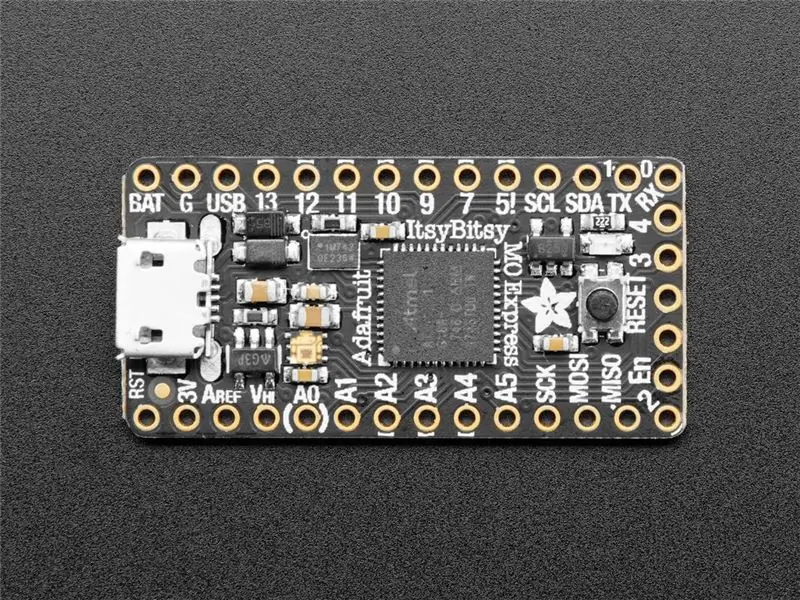

J'aime vraiment le nouveau venu pour les amateurs d'électronique: les microcontrôleurs Atmel SAM D21 basés sur le processeur ARM Cortex M0+ 32 bits fonctionnant à une fréquence d'horloge de 48 MHz, beaucoup plus élevée que les anciens Atmels. Pour ce projet j'ai acheté:

- Carte MCU ItsyBitsy M0 Express d'Adafruit

- J'avais une batterie LiPo rechargeable d'Adafruit

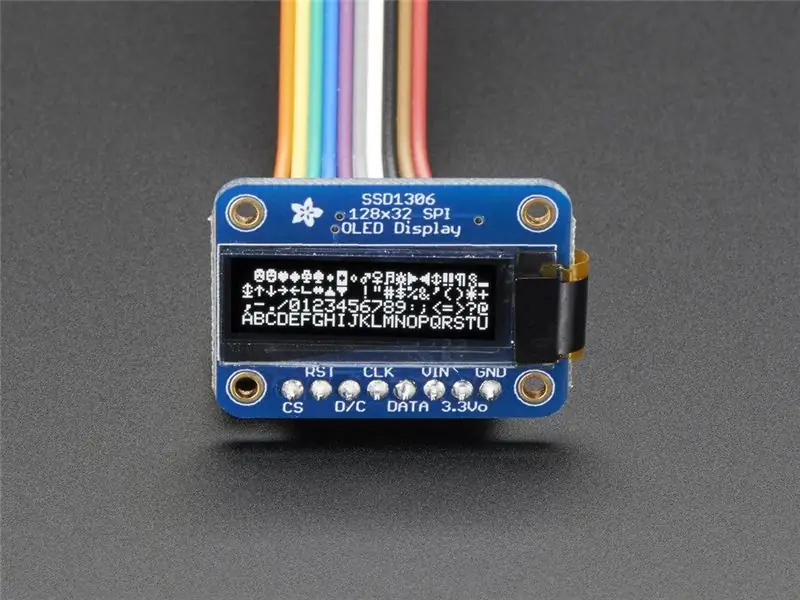

- Écran OLED monochrome 128x32 SPI (vous l'aurez deviné: Adafruit)

- Double bascule JK déclenchée sur front positif SN74HC109 de Texas Instruments

- Double bascule JK déclenchée sur front négatif SN74HC112 de Texas Instruments

- Quadruple ET porte CD74AC08E de Texas Instruments

- Quadruple OU porte CD74AC32E de Texas Instruments

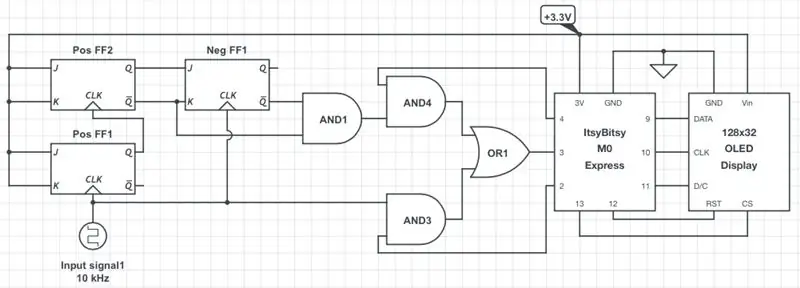

Étape 3: Le circuit

La première figure montre un schéma simplifié du fréquencemètre/dutymètre. La logique CMOS 3,3 V est supposée partout. Par conséquent, l'amplitude de l'onde carrée d'entrée doit être comprise entre le V correspondantHI (c'est-à-dire 2 V) et 3,3 V. Sinon, vous devez l'augmenter ou le réduire en conséquence. Dans la plupart des cas, un simple diviseur de tension suffirait. Si vous souhaitez concevoir votre version du compteur à un niveau logique différent, vous devez utiliser un autre microcontrôleur (MCU), une batterie et un écran qui fonctionnent au niveau souhaité. Les portes logiques et les bascules utilisées dans ce projet fonctionnent avec des niveaux logiques compris entre 2 V et 6 V et devraient fonctionner correctement dans la plupart des cas.

Comme indiqué, le MCU ItsyBitsy utilise les broches 9 à 13 pour communiquer avec l'écran via le protocole logiciel SPI. La broche 3V alimente l'ensemble du circuit. La broche d'entrée numérique 3 accepte le signal analysé, tandis que les broches 2 et 4 contrôlent la source du signal: soit un signal direct provenant de la porte AND3 (fréquences d'entrée basses), soit un signal divisé par 4 via la porte AND4 (fréquences d'entrée élevées) comme décrit à l'étape 2 Le code, abordé à l'étape suivante, détecte automatiquement la gamme de fréquences entrantes et commute de manière appropriée la source du signal.

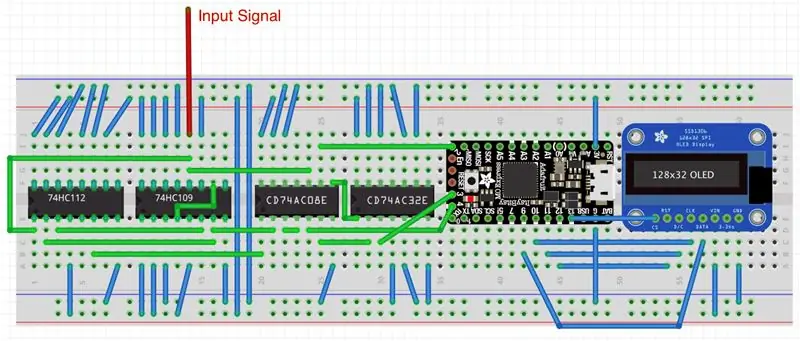

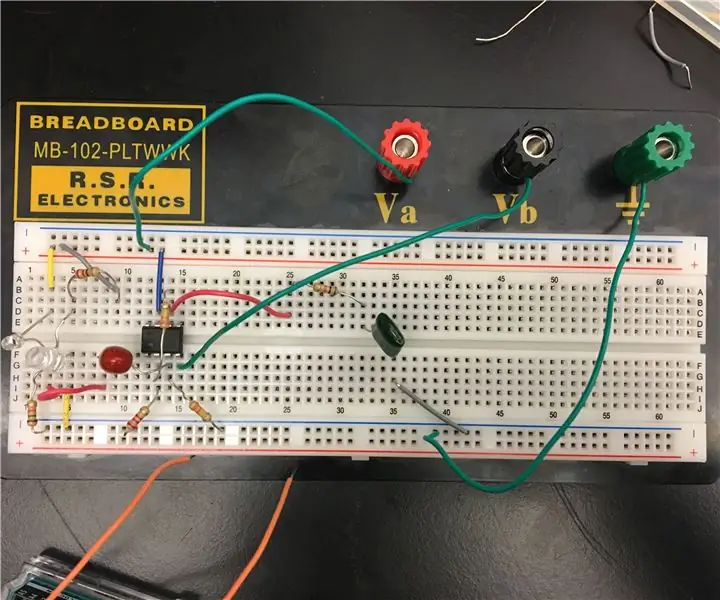

Le schéma ne montre pas la véritable complexité des connexions de puces numériques. La deuxième image montre à quoi ressemblerait le projet sur une maquette. Le signal d'entrée passe par un fil rouge jusqu'à la broche 2CLK de la bascule à double front positif. ATTENTION: Normalement, toutes les broches J et K de cette bascule doivent être maintenues hautes, mais SN74HC109 en particulier comporte la broche Kbar - une broche K inversée - à la place. Par conséquent, cette broche doit être mise à la terre ! La première bascule à front négatif du SN74HC112 a ses broches 1K et 1J connectées aux broches 1Q et 1Qbar du SN74HC109. La deuxième bascule du SN74HC112 est inutilisée et ses broches d'entrée (2K, 2J, 2CLRbar) sont mises à la terre. Toutes les autres broches supplémentaires PREbar (préréglé) et CLRbar (clair) dans toutes les bascules doivent être connectées au niveau logique haut. Les broches d'horloge et de sortie non utilisées ne sont pas connectées. De même, les broches d'entrée inutilisées de toutes les portes sont mises à la terre, tandis que les broches de sortie inutilisées restent non connectées. Comme je l'ai discuté dans mon Instructable « Invisible Killer of the Phone Ring », la mise à la terre des broches d'entrée inutilisées des puces logiques élimine les oscillations aléatoires et économise l'énergie de la batterie.

Étape 4: Le code et la mesure des basses fréquences

Naturellement, toute l'action se passe dans le code lié ci-dessous. Lorsque l'entrée entrante sur la broche 3 passe du numérique bas au haut, le MCU commence à compter les impulsions de son horloge interne de 48 MHz. Il note le moment de la transition de haut en bas et continue le décompte jusqu'au prochain commutateur bas à haut, lorsqu'il redémarre l'ensemble du processus. Le premier compte représente la largeur d'impulsion, tandis que le compte entier représente la période du signal. Et c'est tout le secret.

La CPU note ces transitions via des interruptions matérielles. Le SAMD21 possède plusieurs horloges; mon code utilise un TC3. Au départ, j'ai commencé par lire la fiche technique du M0, ce qui me préparait à beaucoup d'efforts pour coder le gestionnaire d'interruption, mais j'ai rapidement découvert un code très similaire dans les messages du forum Arduino des utilisateurs electro_95, MartinL et Rucus dont la contribution est dûment reconnu. J'ai incorporé et modifié leur code combiné dans le mien; me fait gagner beaucoup de temps !

Comme je l'ai mentionné précédemment, la résolution du signal est limitée à environ 106 cycles CPU pour exécuter le code entre les interruptions. La division numérique avec préservation de la largeur d'impulsion prend en charge les hautes fréquences. Les basses fréquences, en revanche, posent un autre défi: comme le compteur d'horloge TC3 a une longueur de 16 bits, il déborde après avoir franchi la limite des 65 536 comptes. On peut gérer cette situation en ajoutant une interruption de débordement, mais en choisissant une solution différente: TC3 peut utiliser une horloge CPU pré-échelonnée (c'est-à-dire divisée par logiciel) au lieu de l'horloge matérielle 48 MHz. Ainsi, si la période du signal approche de la limite de débordement, le code peut demander à TC3 d'utiliser des comptes de 24 MHz pour la période suivante et, le tour est joué, le compteur tombe en dessous de 32 768 comptes. Pour des fréquences encore plus basses, le TC3 peut être chargé de compter des impulsions de 12 MHz, etc. Le pré-échelonneur approprié est automatiquement déterminé en fonction de la fréquence du signal, avec hystérésis, afin de maintenir le compteur TC3 dans la limite de débordement. En conséquence, l'extrémité inférieure de la plage de l'appareil est d'environ 43 Hz.

Vous êtes invités à dupliquer le code et à l'utiliser dans votre projet, mais veuillez mentionner sa source lors de la publication des résultats.

Lien vers le code.

Conseillé:

Compteur de fréquence haute résolution : 5 étapes (avec photos)

Compteur de fréquence haute résolution : cette instructable montre un compteur de fréquence réciproque capable de mesurer les fréquences rapidement et avec une précision raisonnable. Il est fabriqué avec des composants standard et peut être fabriqué en un week-end (cela m'a pris un peu plus de temps :-)) EDIT : Le code est maintenant disponible

Mesurer la fréquence du secteur à l'aide d'Arduino : 7 étapes (avec photos)

Mesurer la fréquence du secteur à l'aide d'Arduino : le 3 avril, le Premier ministre indien, Shri. Narendra Modi avait appelé les Indiens à éteindre leurs lumières et à allumer une lampe (Diya) à 21h00 le 5 avril pour marquer la lutte de l'Inde contre le virus Corona. Juste après l'annonce, c'était le grand chaos

Mesurer votre fréquence cardiaque au bout de votre doigt : Approche photopléthysmographique pour déterminer la fréquence cardiaque : 7 étapes

Mesurer votre fréquence cardiaque au bout de votre doigt : Approche de la photopléthysmographie pour déterminer la fréquence cardiaque : Un photopléthysmographe (PPG) est une technique optique simple et peu coûteuse qui est souvent utilisée pour détecter les changements de volume sanguin dans un lit microvasculaire de tissu. Il est principalement utilisé de manière non invasive pour effectuer des mesures à la surface de la peau, généralement

Comment mesurer le facteur de puissance CA à l'aide d'Arduino : 4 étapes

Comment mesurer le facteur de puissance CA à l'aide d'Arduino : Salut à tous ! Il s'agit de mon troisième instructable, j'espère que vous le trouverez informatif :-) Ce sera un instructable sur la façon de faire une mesure de base du facteur de puissance à l'aide d'un Arduino. Avant de commencer, il y a quelques points à garder à l'esprit : cela fonctionnera UNIQUEMENT avec

Câbles Argent Personnalisés Audio/Numérique/Haute Fréquence/GPS : 7 Étapes

Câbles argentés personnalisés Audio/numérique/haute fréquence/GPS : avec de nombreux nouveaux modules audio/vidéo et de nouveaux appareils, à la fois audio pour ipod et maintenant numérique pour vidéo, nous devons connecter nos systèmes à de nouveaux appareils avec des câbles plus complexes. Certains sont très chers… Ce sont des composants indispensables & matériaux pour le projet de construction