Table des matières:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:08.

- Dernière modifié 2025-01-23 14:46.

L'objectif de ce projet est de créer la fonctionnalité d'affichage d'image d'un miroir intelligent. Le miroir est capable d'afficher des prévisions (ensoleillé, partiellement ensoleillé, nuageux, venteux, pluie, tonnerre et neige) et des valeurs de température de -9999° à 9999°. Les valeurs de prévision et de température sont codées en dur comme pour émuler leur analyse à partir d'une API météo.

Le projet utilise une carte Zynq-Zybo-7000 exécutant FreeRTOS et utilise Vivado 2018.2 pour concevoir et programmer le matériel.

Les pièces:

Zynq-Zybo-7000 (avec FreeRTOS)

ACL 19 (640x480)

câble VGA

Miroir acrylique 12" x 18"

Étape 1: Configuration de Vivado

Téléchargez Vivado 2018.2 depuis Xilinx et utilisez la licence Webpack. Lancez Vivado et "Créer un nouveau projet" et donnez-lui un nom. Ensuite, sélectionnez "RTL Project" et cochez "Ne pas spécifier de sources pour le moment". Lors de la sélection d'une pièce, sélectionnez "xc7z010clg400-1" et cliquez sur "Terminer" sur la page suivante.

Étape 2: Empaquetage de l'IP du pilote VGA

Ajoutez le fichier vga_driver.sv aux sources de conception. Ensuite, cliquez sur "Outils" et sélectionnez "Créer et empaqueter une nouvelle adresse IP". Sélectionnez « Emballez votre projet en cours ». Choisissez ensuite un emplacement IP et "Inclure les fichiers.xci". Cliquez sur "OK" dans la fenêtre contextuelle, puis sur "Terminer".

Dans « Etapes d'emballage », accédez à « Examiner et emballer » et sélectionnez « IP de l'emballage ».

Maintenant, le vga_driver devrait être disponible en tant que bloc IP.

Étape 3: IP Zynq

Dans la section "IP Integrator", sélectionnez "Créer une conception de bloc". Ajoutez le "ZYNQ7 Processing System" et double-cliquez sur le bloc. Cliquez sur "Importer les paramètres XPS" et téléchargez le fichier ZYBO_zynq_def.xml.

Ensuite, sous "Configuration PS-PL", ouvrez la liste déroulante "Activation non sécurisée AXI" et cochez "Interface M AXI GP0".

Ensuite, sous "Configuration MIO", ouvrez la liste déroulante "Unité de processeur d'application" et cochez "Timer 0" et "Watchdog".

Enfin, sous "Clock Configuration", ouvrez la liste déroulante "PL Fabric Clocks" et cochez "FCLK_CLK0" et à 100 MHz.

Étape 4: IP GPIO

Ajoutez deux blocs GPIO à la conception de bloc. Les GPIO seront utilisés pour contrôler l'adresse des pixels et les composants RVB des pixels. Configurez les blocs comme indiqué dans les images ci-dessus. Une fois que vous avez ajouté et configuré les deux blocs, cliquez sur « Exécuter l'automatisation de la connexion ».

GPIO 0 - Le canal 1 contrôle l'adresse de pixel et le canal 2 contrôle la couleur rouge.

GPIO 1 - Le canal 1 contrôle la couleur verte et le canal 2 contrôle la couleur bleue.

Étape 5: Bloquer la mémoire

Ajoutez une adresse IP de générateur de mémoire de bloc à la conception de bloc et configurez comme indiqué ci-dessus. Les couleurs des pixels sont écrites dans des adresses mémoire qui sont ensuite lues par le pilote VGA. La ligne d'adresse doit correspondre à la quantité de pixels utilisés, elle doit donc être de 16 bits. Les données sont également de 16 bits puisqu'il y a 16 bits de couleur. Nous ne nous soucions pas de la lecture des bits d'accusé de réception.

Étape 6: Autre IP

Le pdf ci-joint montre la conception de bloc terminée. Ajoutez l'IP manquante et terminez les connexions. Également "Make Externals" pour les sorties couleur VGA et les sorties de synchronisation verticale et horizontale.

xlconcat_0 - Concatène les couleurs individuelles pour former un signal RVB 16 bits qui est introduit dans la RAM de bloc.

xlconcat_1 - Concatène les signaux de colonne et de ligne du pilote VGA et est introduit dans le port B de la RAM de bloc. Cela permet au pilote VGA de lire les valeurs de couleur des pixels.

VDD - Constante HIGH connectée à l'autorisation d'écriture du bloc RAM afin que nous puissions toujours y accéder.

xlslice_0, 1, 2 - Les tranches sont utilisées pour diviser le signal RVB en signaux R, V et B individuels qui peuvent être introduits dans le pilote VGA.

Une fois le Block Design terminé, générez un wrapper HDL et ajoutez le fichier de contraintes.

*Block Design est basé sur le tutoriel écrit par benlin1994*

Étape 7: SDK

Le code qui exécute cette conception de bloc est inclus ci-dessous. Init.c contient les fonctions qui gèrent le dessin (prévisions, nombres, symbole de degré, etc.). La boucle principale dans main.c est ce qui est exécuté lorsque la carte est programmée. Cette boucle définit les valeurs de prévision et de température, puis appelle les fonctions de dessin dans init.c. Il parcourt actuellement les sept prévisions et s'affiche l'une après l'autre. Il est recommandé d'ajouter un point d'arrêt à la ligne 239 afin que vous puissiez voir chaque image. Le code est commenté et vous donnera plus d'informations.

Étape 8: Conclusion

Pour améliorer le projet actuel, on pourrait télécharger des images de prévision préchargées sous forme de fichiers COE vers des générateurs de mémoire de blocs. Ainsi, au lieu de dessiner les prévisions manuellement comme nous l'avons fait dans le code C, on pourrait faire lire les images. Nous avons essayé de le faire mais nous n'avons pas pu le faire fonctionner. Nous avons pu lire les valeurs des pixels et les sortir, mais cela a créé des images désordonnées qui ne ressemblaient en rien à celles que nous avons téléchargées dans la RAM. La fiche technique Block Memory Generator est utile à lire.

Le projet est essentiellement la moitié d'un miroir intelligent car il manque l'aspect connectivité Internet. L'ajout de cela donnerait un miroir intelligent complet.

Conseillé:

Fabriquer une horloge miroir à l'infini : 15 étapes (avec photos)

Faire une horloge miroir à l'infini : Dans un projet précédent, j'ai construit un miroir à l'infini, où mon objectif ultime était d'en faire une horloge. (Faire un miroir coloré à l'infini) Je n'ai pas poursuivi cela après l'avoir construit car, même si cela avait l'air cool, il y avait quelques choses avec e

Faire un cube miroir Infinity FACILE - PAS d'impression 3D et PAS de programmation : 15 étapes (avec photos)

Faire un cube miroir Infinity FACILE | PAS d'impression 3D et PAS de programmation : tout le monde aime un bon cube infini, mais on dirait qu'il serait difficile à fabriquer. Mon objectif pour ce Instructable est de vous montrer étape par étape comment en faire un. Non seulement cela, mais avec les instructions que je vous donne, vous pourrez en faire un o

Miroir de vanité de bricolage en étapes faciles (à l'aide de bandes lumineuses à LED): 4 étapes

Miroir de vanité DIY en étapes faciles (à l'aide de bandes lumineuses à LED) : Dans cet article, j'ai fabriqué un miroir de vanité DIY à l'aide des bandes LED. C'est vraiment cool et vous devez les essayer aussi

Affichage de la température sur l'affichage 3310 Manière graphique : 5 étapes

Temp Disply on 3310 Display Graphic Way: Salut, je suis starkship J'ai une chaîne youtube DONC CE PROJET SUR L'UTILISATION DE NOKIA 3310 DISPLAYSUPPLY:-1 X NOKIA 3310 DISPLAY (ANCIEN/NOUVEAU) 1 X ARDUINO UNO /NANO (TOUS TYPE SONT WORKE) 1X LM35 TEMP SENSOR1 X 10uf (ÉLECTROLYTIQUE CONDENSATEUR) quelques fils

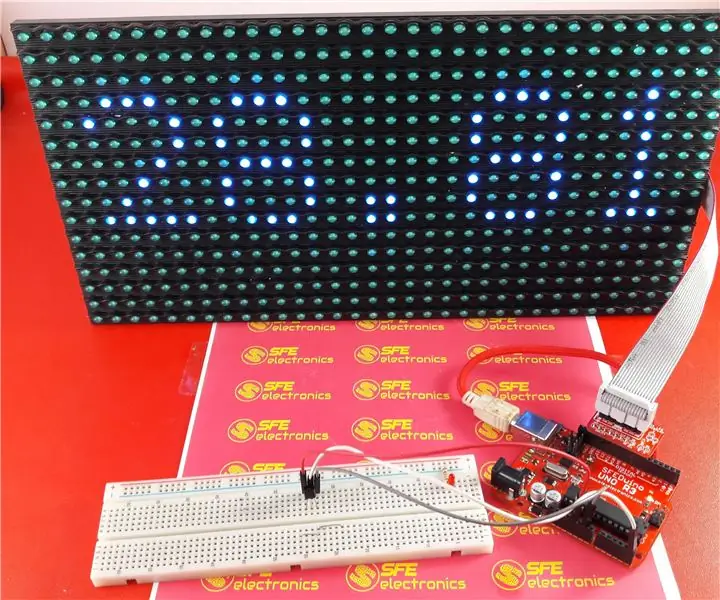

Affichage de la température sur le module d'affichage LED P10 à l'aide d'Arduino : 3 étapes (avec photos)

Affichage de la température sur le module d'affichage à LED P10 à l'aide d'Arduino: Dans le didacticiel précédent, il a été expliqué comment afficher du texte sur le module d'affichage à LED matricielle P10 à l'aide d'Arduino et du connecteur DMD, que vous pouvez vérifier ici. Dans ce didacticiel, nous allons donner un didacticiel de projet simple en utilisant le module P10 comme moyen d'affichage