Table des matières:

- Fournitures

- Étape 1: Configuration requise pour le port série

- Étape 2: Exigences de programmation PIC

- Étape 3: Spécification JDM

- Étape 4: Description du circuit

- Étape 5: Préparez-vous pour la simulation

- Étape 6: Modifications pour ICSP

- Étape 7: Résultats de la simulation

- Étape 8: Conclusions

- Étape 9: Et enfin

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:05.

- Dernière modifié 2025-01-23 14:45.

JDM est un programmeur PIC populaire car il utilise un port série, un strict minimum de composants et ne nécessite aucune alimentation électrique. Mais il y a une confusion là-bas, avec de nombreuses variantes de programmeurs sur le net, lesquelles fonctionnent avec quels PIC ? Dans ce "instructable", nous mettons JDM à l'épreuve et je montre comment simuler le circuit à l'aide de Spice qui répondra à toutes vos questions !

Fournitures

LTspice qui peut être téléchargé depuis Analog Devices ici.

Vous avez également besoin des fichiers du circuit JDM ici.

Étape 1: Configuration requise pour le port série

JDM nécessite un port série conforme à la spécification EIA232, idéalement avec des niveaux de tension +12/-12.

Selon la fiche technique Texas Instruments Line Driver MC1488 (Figure 3)

Impédance de sortie = 4V/8mA = 500 ohm.

Limite de courant de court-circuit = 12 mV, sans limite de temps - aucun dommage à la puce.

Impédance d'entrée du récepteur de ligne = 3k à 7k ohm recommandé.

Les ports série sur les anciens PC de bureau utilisent +12v/-12V répondant à cette exigence.

Les ports série des ordinateurs portables les plus récents utilisent des tensions plus basses. JDM peut fonctionner ou non - la réponse est plus complexe.

Étape 2: Exigences de programmation PIC

Les informations concernant les exigences de programmation PIC sont obtenues auprès de Microchip. Ce qui précède est pour un appareil typique.

Étape 3: Spécification JDM

Le site Web original de JDM a-t-il été perdu dans la nuit des temps ? Cela nous laisse deviner ce que le concepteur avait initialement prévu pour la spécification.

- Prévoir VDD=5V, et jusqu'à IDD=2mA maximum (pour la version « in socket »)

- Fournir VHH=13V, et jusqu'à IHH=0.2mA maximum.

- MCLR Temps de montée tVHHR = 1uS max.

- La version ICSP doit être capable de tirer MCLR bas contre 22k pull-up sur la cible.

Étape 4: Description du circuit

La figure JDM1 est basée sur le circuit JDM « standard » tiré du site Web de PICPgm. Il s'agit du programmeur « PIC in Socket » où le PIC est alimenté par les broches TX et RTS. Le diagramme d'origine était difficile à comprendre, je l'ai donc redessiné en utilisant la convention normale du flux de courant de haut en bas. Et j'ai ajouté des indicateurs LED "RESET", "PROG" et "RTS" qui sont nécessaires pendant la construction et les tests. Espérons que ceux-ci n'auront aucun effet néfaste sur le comportement.

La convention normale de conception de circuit est de mettre en commun toutes les masses, mais la caractéristique clé de JDM est que la masse du port série (GND) est connectée au VDD. Cela crée une confusion car les signaux du port série sont mesurés par rapport à GND, les signaux PIC par rapport à la masse logique (VSS).

Lorsque TX passe au niveau haut, Q1 se comporte comme deux diodes polarisées en direct. (Le collecteur Q1 n'est pas polarisé en inverse comme avec le fonctionnement normal du transistor). Le collecteur Q1 charge C2, qui est fixé à VDD+8V par Zener (D3). L'émetteur Q1 fournit 13 V au MCLR pour le mode programmation/vérification.

Lorsque TX baisse, le condensateur C3 est chargé via D1 et VSS est bloqué à VDD-5V par Zener (D5). De plus, TX est bloqué à (VSS-0.6) par D1. Q1 est éteint, C1 conserve sa charge pour la prochaine impulsion de programmation. Le MCLR est bloqué à 0V par D2, donc le PIC est maintenant réinitialisé.

Lorsque RTS est élevé, l'horloge est transmise au PGC. D4 pince PGC au niveau logique VDD haut. Lorsque RTS est bas, le condensateur C3 est chargé via D6 et VSS est bloqué à VDD-5V par Zener (D5). D6 bloque PGC à VSS ou 0 logique.

Lors de la programmation, les données envoyées sur DTR sont lues sur PGD, que le PIC configure en entrée. Lorsque le DTR est élevé, Q2 agit comme « suiveur d'émetteur » et la tension PGD est d'environ (VDD-0.6) ou logique 1. Lorsque DTR est faible, Q2 agit comme un mauvais transistor (broches émetteur et collecteur inversées). Q2 tire PGD bas, qui est bloqué par D7 à VSS ou 0 logique.

Pendant la vérification, le PIC configure PGD comme sortie pour envoyer des données au port série. Le DTR doit être élevé et les données sont lues sur le CTS. Lorsque la sortie PGD est élevée, Q2 est désactivé, CTS = DTR = +12V. Lorsque la sortie PGD est faible, Q2 est activé. Le collecteur Q2 tire le courant (12V+5V)/(1k+1k5)=7mA du DTR, et tire le CTS bas, vers VSS.

Étape 5: Préparez-vous pour la simulation

Téléchargez LT spice, enregistrez et ouvrez les fichiers de circuit (*.asc) fournis ici. Pour simuler le circuit, il faut lui donner quelques entrées, puis « tracer » les sorties. V1, V2 V3 simulent le port série 12V avec l'impédance de sortie R11, R12, R13.

- V1 génère 2 impulsions de programme sur TX de 0,5 ms à 4,5 ms

- V2 génère une rafale d'impulsions de données sur DTR de 1,5 à 4,5 ms

- V3 génère des rafales d'impulsions d'horloge sur RTS de 0,5 à 3,5 ms

Les composants V4, X1, R15 et R16 font tous partie de la simulation.

- V4 génère 2 impulsions de 2,5 à 4,5 ms pour vérifier les données.

- Le cavalier X1 simule la SORTIE sur PGD.

- R15, R16 simulent le « chargement » du PIC sur VDD et MCLR.

Étape 6: Modifications pour ICSP

La figure JDM3 montre la version pour la programmation « en circuit ». Les modifications par rapport à l'original sont

- Remplacez la prise ZIF par le connecteur ICSP.

- Le PIC est maintenant alimenté par l'alimentation du circuit cible (V5).

- Retirez le Zener 5V (D5).

- Le petit condensateur de 100pF (C4) est déplacé à côté du PIC sur le circuit cible.

- Les LED sont alimentées par le circuit imprimé dans la mesure du possible.

- La résistance de rappel MCLR (R10) et la diode (D10) sont requises sur le circuit cible.

- ATTENTION. La carte cible doit avoir une alimentation "flottante", idéalement une batterie.

- Ne connectez pas la terre cible (VSS) à la terre de l'ordinateur/PC en connectant d'autres ports d'ordinateur en même temps que JDM.

Après avoir simulé JDM1, le problème du long temps de charge sur C2 est devenu apparent. Ensuite, après avoir lu Fruttenboel, il apparaît que C2 et Q1 ont été ajoutés en tant que modification à l'original. Je ne peux pas penser à ce que C2 et Q1 sont censés faire à part créer des problèmes. Donc, pour JDM4, nous revenons à l'ancienne conception sur Fruttenboel qui est simple et directe à comprendre. D1 et D3/LED2 pince MCLR entre VSS et VDD+8V. La valeur de R1 est réduite à 3k3, juste suffisante pour éclairer LED2 à 12V.

JDM4 est également conçu pour fonctionner avec des ports série plus faibles. Lorsque TX passe au niveau haut (+9V), source de courant TX = (9-8)/(1k +3k3) = 0,2ma, juste assez pour tirer le MCLR haut bien qu'insuffisant pour éclairer la LED2. Lorsque TX devient faible (environ -7V), le puits de courant TX =(9-7)/1k = 2mA. Courant LED1 = (7-2 pour led)/(2k7) = 1,8mA. Courant d'abaissement MCLR = 7-5,5/3k3 = 0,5 mA.

Ce circuit a également été testé (simulation JDM5) pour voir ce qui se passe avec les ports série +/-7V minimum, où la tension est insuffisante pour soutenir VHH=13V. Le but de C1 devient maintenant évident, C1 crée un court +ve boost à MCLR, un pic de 33us sur le front montant de TX, suffisamment long pour que le PIC entre en mode programmation, peut-être ? Mais retirez le cavalier X2 (désactivez la LED1) car le courant est insuffisant pour tirer le MCLR au niveau bas et allumer la LED1 ensemble. Lorsque TX devient faible, le puits de courant TX = (7V-5,5V)/(1k+3k3) = 0,3mA, juste suffisant pour tirer MCLR bas contre le pull-up R10.

Étape 7: Résultats de la simulation

Pour visualiser les fichiers graphiques, il est préférable de faire un clic droit sur les liens ci-dessous, puis de sélectionner "Ouvrir le lien dans un nouvel onglet"

Simulation 1: trace de MCLR, VSS et RTS pour le JDM1 d'origine. Immédiatement les observations 1, 2 et 3 sont apparentes.

Simulation 2: trace de MCLR et VSS, et RTS pour JDM2 modifié, ce qui corrige les problèmes précédents.

Simulation 3: trace de PGD, VSS et PGC pour JDM2 envoyant des données en mode programme. Observation 4 à 3,5 mS.

Simulation 4: trace de PGD, VSS et CTS pour JDM2 en mode vérification (cavalier X1 inséré). d'accord

Simulation 5: trace de MCLR, VSS, PGD et PGC pour JDM3. ICSP utilisant l'alimentation du circuit résout de nombreux problèmes.

Simulation 6: trace de MCLR, VSS, PGD et PGC pour JDM4 avec port série +/-9V. MCLR monte immédiatement, pleinement fonctionnel.

Simulation 7: trace de MCLR, VSS et TX pour JDM5 avec port série +/-7V et cavalier X2 retirés. C1 crée un boost +ve (pic) sur le front montant de MCLR, à peu près suffisant pour pousser MCLR au-dessus de TX à 13V.

Étape 8: Conclusions

Spice est vraiment bon pour révéler les « secrets cachés » du fonctionnement du circuit. Evidemment le circuit JDM fonctionne et est compatible avec de nombreuses puces PIC, mais les observations suivantes révèlent de possibles limitations/problèmes de compatibilité/défauts ?

- Long temps de montée de MCLR pendant que C2 se charge à VPP sur la première impulsion de TX. Échec de la spécification 3.

- Le port série charge C2 lorsque TX devient élevé et RTS devient faible. Mais RTS a aussi pour mission de charger C3. Lorsque les deux se produisent en même temps, cela crée plus de charge sur RTS, par conséquent C3 perd sa charge (VSS augmente) à 2 ms lors de la simulation. Échec de la spécification 1.

- C3 perd sa charge (VSS commence à augmenter) après l'arrêt des impulsions d'horloge à 3,5 ms.

- Quel est le but de C2, est-il nécessaire du tout ?

Solutions

- Vraisemblablement, PICPgm utilise un logiciel "work-round". Il doit appliquer une longue impulsion TX pour précharger à C2, puis entrer en mode programmation uniquement après la deuxième impulsion TX ? Pour la simulation, j'ai réduit la valeur de C2 à 1 uF pour donner un temps de montée de 1 ms. Pas une solution idéale.

- Divisez C2 et C3 pour qu'ils se chargent indépendamment. Une petite modification de JDM2, C2 est référencé à GND au lieu de VSS.

- Résolu par JDM3. ICSP est beaucoup plus fiable car le PIC est alimenté par le circuit cible.

- JDM4 résout le problème 1. Il s'agit d'une conception simple éliminant complètement C2.

Étape 9: Et enfin

La preuve du pudding est dans l'alimentation. Ce JDM fonctionne donc continuez à l'utiliser.

Et mes recommandations sont:

- utilisez JDM2 pour la programmation en socket et les ports série 12V,

- utilisez JDM4 pour le programmeur ICSP et les ports série supérieurs à +/- 9 V,

- utilisez JDM4 avec le cavalier X2 retiré pour les ports série au-dessus de +/-7V.

Les références:

Piment Analog Devices LT

picpgm

Fruttenboel

Suivez plus de projets PIC sur sly-corner

Conseillé:

Arduino en tant que FAI -- Graver un fichier hexadécimal dans AVR -- Fusible dans l'AVR -- Arduino en tant que programmeur : 10 étapes

Arduino en tant que FAI || Graver un fichier hexadécimal dans AVR || Fusible dans l'AVR || Arduino en tant que programmeur :………………………Veuillez vous abonner à ma chaîne YouTube pour plus de vidéos……..Cet article est tout à propos d'arduino en tant que fournisseur d'accès Internet. Si vous souhaitez télécharger un fichier hexadécimal ou si vous souhaitez configurer votre fusible dans l'AVR, vous n'avez pas besoin d'acheter un programmeur, vous pouvez le faire

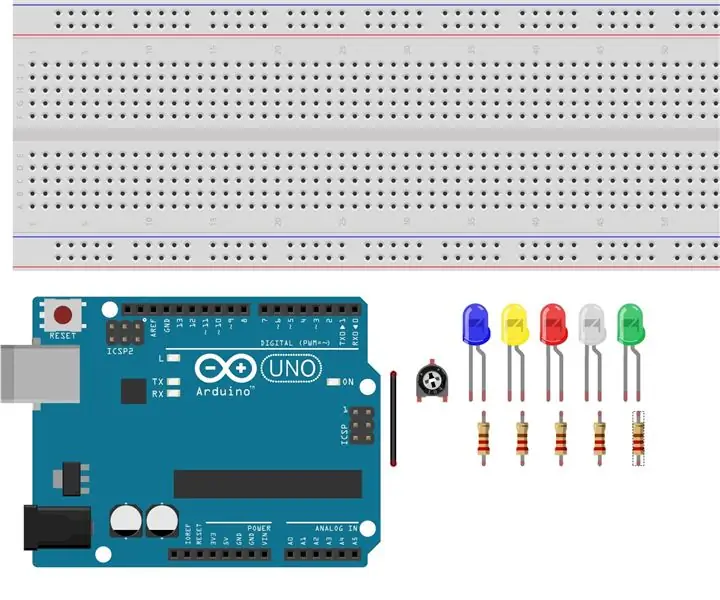

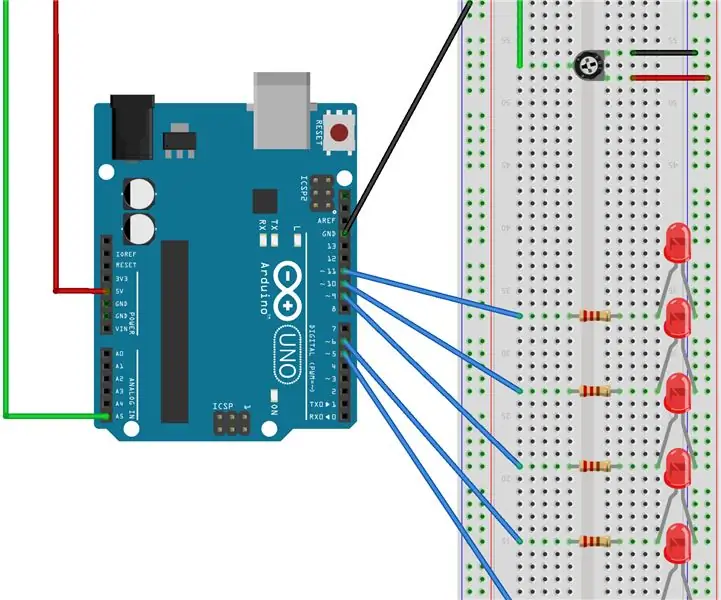

Contrôle LED avec potentiomètre - Examen final : 3 étapes

Contrôle LED avec potentiomètre - Examen final : Pour mon projet d'examen final, j'ai créé un contrôleur LED à l'aide d'un potentiomètre. Le but de ce projet est d'utiliser le potentiomètre pour contrôler quelles LED sont allumées. Lorsque le potentiomètre est tourné dans le sens des aiguilles d'une montre, il éteint les LED pour que la première LED

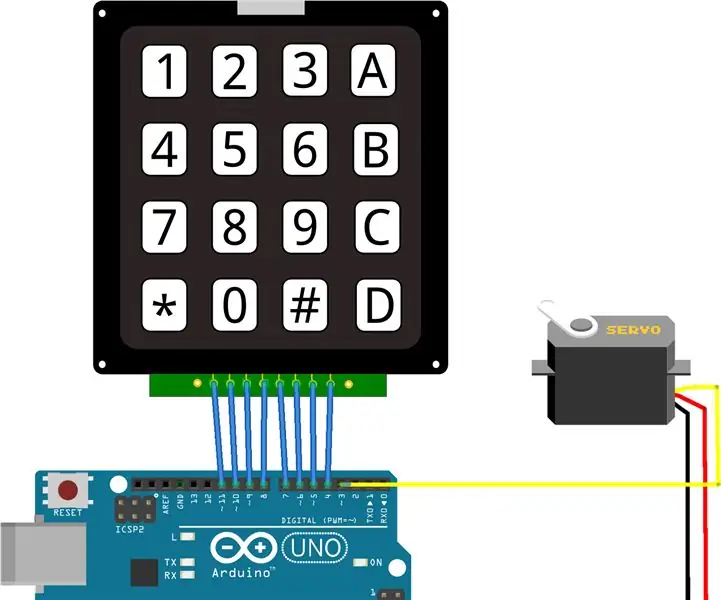

Projet d'examen final CSCI-1200 2: 3 étapes

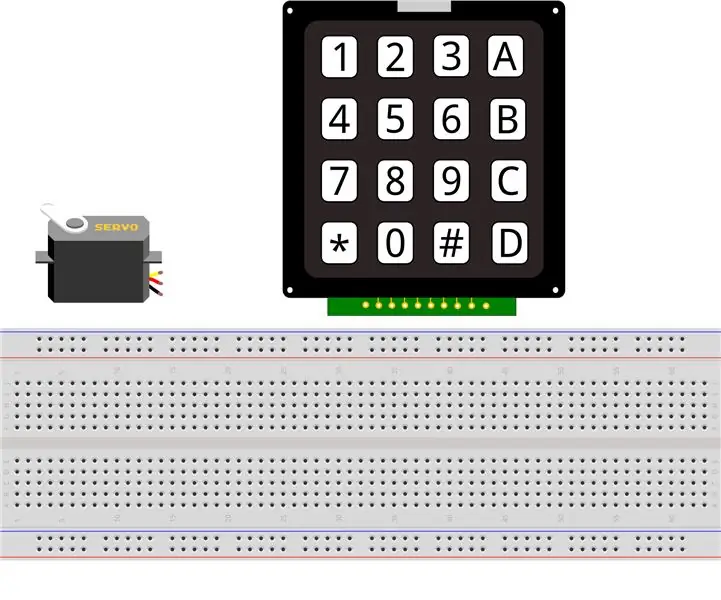

CSCI-1200 Final Exam Project 2: Dans ce laboratoire, vous utiliserez un clavier 4x4 pour changer l'angle d'un servomoteur. L'angle sera déterminé par une entrée à 3 chiffres à l'aide du clavier. Le clavier n'acceptera pas de valeurs non numériques. Matériel requis pour ce projet : 1. Arduino Uno2. 4x4 k

Projet d'examen final CSCI-1200 1: 3 étapes

CSCI-1200 Final Exam Project 1 : Dans ce laboratoire, vous utiliserez un potentiomètre pour allumer et éteindre 5 LED. Les LED incluront un fondu pour que la LED sélectionnée soit la plus lumineuse, tandis que les autres LED sont éteintes ou légèrement plus faibles. Matériel requis pour ce projet : 1. Arduino Un

Examen final - Projet 2 : 3 étapes

Examen final - Projet 2 : Pour cet exercice, nous utiliserons un pavé numérique pour écrire des angles sur notre servomoteur. Spécifiquement pour ce projet, vous aurez besoin de:1 microcontrôleur Arduino1 planche à pain pleine grandeur1 membrane/clavier numérique1 servomoteurUn paquet de fils de cuivre