Table des matières:

- Étape 1: Schéma fonctionnel

- Étape 2: Principe de fonctionnement

- Étape 3: Implémentation de la logique

- Étape 4: Résoudre l'impasse

- Étape 5: Configuration de l'appareil - Circuit Matrix0

- Étape 6: Configuration de l'appareil - Logique d'horloge SPI

- Étape 7: Configuration de l'appareil - Propriétés des composants Matrix0

- Étape 8: Configuration de l'appareil - Circuit Matrix1

- Étape 9: Configuration de l'appareil - Compteur binaire 3 bits

- Étape 10: Configuration de l'appareil - Logique de comparaison 3 bits

- Étape 11: Configuration de l'appareil - Logique de comparaison numérique et registre temporaire

- Étape 12: Configuration de l'appareil - Propriétés des composants Matrix1

- Étape 13: Résultats

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:06.

- Dernière modifié 2025-01-23 14:45.

Les systèmes de contrôle et les dispositifs associés traitent de multiples sources d'alimentation, telles que des lignes de polarisation ou des batteries, et doivent suivre la ligne la plus élevée (ou la plus basse) parmi un ensemble donné.

Par exemple, la commutation de charge dans un système alimenté par « multi-batteries » nécessite que le système surveille la tension minimale ou maximale parmi le réseau de batteries (max ou min en fonction de l'algorithme de commutation particulier) et achemine dynamiquement la charge vers le source la plus appropriée en temps réel. Alternativement, le système peut avoir besoin de déconnecter temporairement la batterie la plus basse tension pour une charge correcte.

Un autre exemple est le système d'énergie solaire moderne, où chaque panneau solaire est équipé d'un mécanisme d'inclinaison et d'un circuit de suivi solaire (ce dernier fournissant l'information sur la position du soleil pour orienter le panneau). Avec les informations de tension maximale, chaque position de panneau solaire peut être affinée sur la base du panneau de la chaîne fournissant réellement la tension de sortie la plus élevée, atteignant ainsi un niveau supérieur d'optimisation de la puissance.

Il existe plusieurs marques différentes de circuits intégrés commerciaux (principalement des microcontrôleurs) qui peuvent en principe implémenter un suiveur de tension maximale. Cependant, ils nécessitent une programmation et sont moins rentables qu'une solution à signaux mixtes. Compléter une conception Dialog GreenPAKTM peut avoir un impact positif sur l'abordabilité, la taille et la modularité de la conception. Cette conception exploite l'avantage d'intégrer à la fois des circuits analogiques et numériques dans une seule puce.

Dans ce Instructable, le frontal analogique et la logique numérique nécessaires pour mettre en œuvre un chercheur de tension max (ou éventuellement min) parmi huit sources distinctes est mis en œuvre.

Pour mettre en œuvre le moniteur de tension max/min analogique à 8 canaux, un SLG46620G est utilisé.

Ci-dessous, nous avons décrit les étapes nécessaires pour comprendre comment la solution a été programmée pour créer le moniteur de tension analogique max/min à 8 canaux. Cependant, si vous souhaitez simplement obtenir le résultat de la programmation, téléchargez le logiciel GreenPAK pour afficher le fichier de conception GreenPAK déjà terminé. Branchez le kit de développement GreenPAK à votre ordinateur et appuyez sur programme pour créer le moniteur de tension analogique max/min à 8 canaux.

Étape 1: Schéma fonctionnel

La figure 1 montre le schéma global du système mis en œuvre.

Une chaîne de jusqu'à 8 sources de tension variable est multiplexée et interfacée à un module ADC GreenPAK connecté à une conception interne personnalisée capable de sélectionner la source avec la tension la plus élevée par rapport aux autres. La logique interne sort ces informations pour affichage ou traitement ultérieur.

La conception est basée sur le produit GreenPAK SLG46620G, car il intègre tous les blocs de construction analogiques et numériques nécessaires à l'application. Dans cette mise en œuvre, le réseau est balayé au moyen d'un multiplexeur analogique ADG508 directement piloté par le circuit intégré GreenPAK.

Les informations de sortie sont un nombre numérique à 3 bits correspondant au nombre de source de tension à la tension maximale. Un moyen direct d'obtenir cette information est d'afficher le numéro au moyen d'un affichage à 7 segments. Cela peut être facilement réalisé en interfaçant la sortie numérique du SLG46620G à un pilote d'affichage à 7 segments, tel que la solution GreenPAK décrite dans la référence ou à un circuit intégré 74LS47 commun.

Le circuit présenté recherche la tension maximale. Pour convertir la conception en un détecteur de tension minimale, un simple circuit de préconditionnement doit être ajouté entre le multiplexeur analogique et l'entrée analogique GreenPAK, en soustrayant la sortie du multiplexeur d'une tension de référence de 1 V.

Étape 2: Principe de fonctionnement

La conception vise à sélectionner la source avec une tension maximale, donc un balayage est effectué sur l'ensemble du réseau tout en stockant la dernière valeur max et en la comparant avec la valeur suivante en entrée (qui appartient à la prochaine source de tension dans le balayage).

Dans ce qui suit, nous ferons référence à une séquence de multiplexage complète le long de toutes les entrées sous le nom de « balayage » ou « boucle ».

La comparaison entre deux valeurs n'est pas réalisée au moyen de composants ACMP (cependant, disponible dans le SLG46620G), mais plutôt par le module DCMP, une fois les valeurs respectivement numérisées. Il s'agit d'une technique avancée et raffinée abordée pour la première fois dans Référence.

La figure 2 montre comment le SLG46620G est structuré pour cette conception.

Le signal d'entrée analogique va à l'entrée ADC via le composant PGA avec un gain défini de 1. Divers réglages de gain sont également possibles pour trouver la meilleure correspondance avec l'électronique de conditionnement frontale dédiée à la cartographie des tensions d'entrée sur le 0-1 V gamme du module GreenPAK ADC.

L'ADC fonctionne en mode asymétrique et convertit le signal analogique en un code numérique à 8 bits, qui est ensuite transféré au module DCMP. Le code numérique est également introduit dans le bloc SPI, configuré comme un tampon ADC/FSM, où un code numérique peut être stocké et ne changera pas jusqu'à ce que la prochaine impulsion arrive à l'entrée SPI CLK. Notez qu'un bloc logique dédié pilote l'entrée SPI CLK. Nous étudierons cette partie plus tard, car c'est la logique « noyau » responsable du bon fonctionnement. Un nouveau code numérique est stocké dans le module SPI uniquement s'il appartient à la tension d'entrée maximale réelle.

Le composant DCMP est utilisé pour comparer les données ADC actuelles avec le dernier gagnant (c'est-à-dire le dernier max trouvé) qui est stocké dans le bloc SPI. Il générera une impulsion à la sortie OUT+ lorsque la nouvelle donnée ADC est supérieure à la précédente. Nous utilisons le signal OUT+ pour mettre à jour le bloc SPI avec le nouveau gagnant.

Un signal d'horloge global pilote les conversions ADC et les synchronisations générales. Une fois la conversion effectuée, le signal de sortie INT de l'ADC émet des impulsions, coordonnées dans le temps avec la sortie de données parallèle de l'ADC. Nous utilisons également la sortie INT pour incrémenter un compteur binaire à 3 bits, implémenté par les DFF dans Matrix1, ce qui est utile pour trois raisons:

1. Les lignes de sortie du compteur adressent le multiplexeur analogique externe, servant ainsi la prochaine tension d'entrée à l'ADC;

2. Le compte est gelé dans un registre à 3 bits (implémenté dans Matrix1) pour stocker le gagnant temporaire lors d'un balayage;

3. Le compte est décodé pour mettre à jour un deuxième registre à 3 bits (implémenté dans Matrix0) une fois qu'un balayage est terminé.

Étape 3: Implémentation de la logique

Le module ADC fournit séquentiellement les données converties de toutes les tensions d'entrée, l'une après l'autre, indéfiniment. Une fois que le multiplexeur est adressé à 0b111 (décimal 7), le compteur passe à 0b000 (décimal 0) commençant ainsi une nouvelle scrutation des tensions d'entrée.

Pendant le balayage, le signal de sortie ADC INT est généré lorsque la sortie de données parallèle est valide. Lorsque ce signal émet des impulsions, le multiplexeur analogique doit passer à l'entrée suivante, fournissant au PGA la tension correspondante. Par conséquent, la sortie ADC INT est le signal d'horloge direct du compteur binaire à 3 bits de la figure 2, dont le mot de sortie parallèle à 3 bits adresse directement le multiplexeur analogique externe ("V select" sur la figure 1).

Référons-nous maintenant à un exemple où les tensions d'entrée sont supposées avoir les relations suivantes:

a) V0 < V1 < V2

b) V2 > V3, V4

c) V5 > V2

La figure 3 représente les principaux signaux impliqués dans le mécanisme de décision max.

Étant donné que les données sont finalement synchronisées dans le registre tampon SPI de manière synchrone avec les impulsions INT, une fenêtre de comparaison existe dans laquelle le contenu du tampon SPI est comparé au résultat de conversion ADC suivant. Cette temporisation particulière entraîne la génération d'impulsions OUT+ à la sortie DCMP. Nous pouvons profiter de ces impulsions pour charger de nouvelles valeurs dans le registre tampon SPI.

Comme il ressort de la ligne de données du tampon SPI de la figure précédente, le registre SPI contient toujours, temps par temps, la plus grande valeur parmi les 8 entrées et il n'est mis à jour que lorsqu'une plus grande valeur est détectée par le module DCMP (en référence au DCMP OUT+ ligne de sortie du tracé, les impulsions manquantes font que V2 reste verrouillé dans le registre jusqu'à ce qu'il soit comparé à V5).

Étape 4: Résoudre l'impasse

Si la logique implémentée était telle que décrite ci-dessus, il est clair que nous nous retrouverions dans une situation de blocage: le système n'est capable de détecter que des tensions supérieures à celle correspondant à ce qui est stocké dans le registre tampon SPI.

Ceci est également valable dans le cas où cette tension diminuerait et qu'une autre entrée, jusqu'à présent inférieure à celle-ci, deviendrait la plus élevée: elle ne serait jamais détectée. Cette situation est mieux expliquée sur la figure 4 où seules 3 tensions d'entrée sont présentes par souci de clarté.

Au moment de l'itération 2, V3 chute et V1 est la tension maximale réelle. Mais le module DCMP ne fournit pas d'impulsion car les données stockées dans le registre tampon SPI (correspondant à 0,6 V) sont plus grandes que celles correspondant à V1 (0,4 V).

Le système se comporte alors comme un Finder max « absolu » et ne met pas à jour correctement la sortie.

Un bon moyen de surmonter ce problème consiste à forcer le rechargement des données dans le registre tampon SPI lorsque le système termine un cycle d'interrogation complet de tous les canaux.

En fait, si la tension à cette entrée est toujours la plus élevée, rien ne change et le contrôle continue en toute sécurité (en référence à la figure 4 ci-dessus, c'est le cas des itérations de boucle 0 et 1). En revanche, si la tension à cette entrée descend par hasard à une valeur inférieure à une autre entrée, alors le rechargement de la valeur donne la possibilité au module DCMP de produire une impulsion OUT+ en la comparant avec la nouvelle valeur max (c'est la cas des itérations de boucle 2 et 3).

Un morceau de circuit logique est nécessaire pour surmonter le problème. Il doit générer un signal d'horloge vers le composant SPI lorsque la boucle atteint l'entrée max réelle, forçant ainsi un rechargement de son mot de données mis à jour dans le registre tampon SPI. Ceci sera discuté dans les sections 7.2 et 7.6 ci-dessous.

Étape 5: Configuration de l'appareil - Circuit Matrix0

Le SLG46620G possède deux blocs Matrix, comme illustré à la Figure 2. Les Figures suivantes montrent les configurations respectives des appareils.

La partie haute du circuit est le « Loop Register » réalisé avec 3 DFF (DFF0, DFF1 et DFF2). Il est rafraîchi après chaque boucle du multiplexeur d'entrée pour envoyer à un pilote d'affichage à 7 segments le nombre binaire du « gagnant », c'est-à-dire l'entrée avec la tension la plus élevée lors du dernier balayage. L'horloge des DFF et les données proviennent de la logique implémentée dans Matrix1 via, respectivement, les ports P12, P13, P14 et P15.

La partie inférieure est le frontal analogique avec entrée sur la broche 8 et PGA avec gain x1. La sortie ADC INT va à la fois à la logique d'horloge de SPI et à Matrix1 via le port P0, où elle servira de signal d'horloge pour le compteur mis en œuvre.

Les sorties de données parallèles ADC et SPI sont respectivement étiquetées NET11 et NET15 pour être connectées au composant DCMP dans Matrix1.

Étape 6: Configuration de l'appareil - Logique d'horloge SPI

Comme indiqué précédemment dans la section « Implémentation de la logique », le registre tampon SPI est mis à jour chaque fois qu'une comparaison entre la valeur réelle stockée et les nouvelles données de conversion ADC génère une impulsion à la sortie DCMP OUT+.

L'intégrité du signal est assurée si ce signal est effectué par ET avec la sortie ADC INT. Cela évite tout pic et faux déclenchement.

Nous avons également souligné que pour éviter les situations de blocage, le tampon SPI doit être mis à jour lorsque la boucle atteint les données réelles du gagnant.

Trois signaux sont alors en jeu pour une synchronisation SPI correcte:

1. Sortie ADC INT (LUT0-IN1)

2. Sortie DCMP OUT+ (LUT0-IN0 via le port P10)

3. Le nombre est égal au signal de verrouillage (LUT0-IN2 via le port P11)

Les deux premiers sont traités par ET et tous deux par OU avec le dernier dans LUT0, dont l'implémentation est configurée comme dans la figure 6.

Étape 7: Configuration de l'appareil - Propriétés des composants Matrix0

Les figures 7 à 10 montrent les autres fenêtres de propriétés des composants appartenant à Matrix0.

Étape 8: Configuration de l'appareil - Circuit Matrix1

Étape 9: Configuration de l'appareil - Compteur binaire 3 bits

La partie supérieure du circuit contient des éléments logiques, principalement un compteur binaire à 3 bits cadencé par la sortie ADC INT, comme déjà évoqué. Ce compteur est implémenté avec un schéma assez « standard » représenté sur la figure 12.

Ce compteur est réalisé dans notre conception au moyen de Flip-Flops DFF9, DFF10, DFF11 et INV1, LUT4, LUT8. La sortie DFF9 est le LSB tandis que DFF11 est le MSB, comme le montre la Figure 13.

LUT4 est configuré en tant que XOR tandis que LUT8 exécute la logique AND-XOR de la figure 12.

Les sorties de compteur vont à trois broches de sortie numérique pour adresser le multiplexeur analogique externe.

LUT10 décode le code du compteur lorsqu'un balayage est terminé et envoie une impulsion à Matrix0 via DLY8 et le port P12. Ceci est simplement accompli en effectuant une opération ET sur les sorties du compteur, décodant ainsi le numéro 7 déc (0b111 binaire, fin de boucle).

Étape 10: Configuration de l'appareil - Logique de comparaison 3 bits

La figure 15 montre le circuit utilisé pour détecter quand la boucle est en train d'itérer à l'adresse « gagnante » actuelle. Dans ce cas, comme déjà discuté, une impulsion numérique devrait forcer un rechargement du résultat ADC actuel pour résoudre une éventuelle situation de blocage.

L'adresse « gagnant » est stockée dans le registre temporaire de Matrix1 (voir ci-dessous), tandis que l'adresse actuelle est sortie par le compteur binaire.

Les portes XNOR fournissent une sortie vraie (logique 1 ou « haute ») lorsque les deux entrées sont égales. L'opération ET de ce signal pour tous les bits (LUT9) nous donne une impulsion lorsque les deux codes binaires sont identiques. Des détails sur les portes XOR en tant que vérificateur de parité peuvent être trouvés dans la référence.

Le signal « Counter-equals-Latch » est transmis à Matrix0 via le port P11.

Étape 11: Configuration de l'appareil - Logique de comparaison numérique et registre temporaire

La partie inférieure de la figure 11 (mise en évidence sur la figure 16) montre le bloc DCMP, la partie décisionnelle de cette conception.

DFF6, 7 et 8 forment un registre à 3 bits pour stocker le numéro d'entrée temporaire « gagnant » pendant l'exécution de la boucle. Les entrées des bascules sont les sorties du compteur binaire à 3 bits, comme visible dans le circuit global Matrix1 de la figure 11, ici ignorées par souci de clarté.

Les sorties de ce registre ne peuvent pas piloter directement l'affichage à 7 segments car la valeur stockée ici change au cours d'un balayage et ne doit être considérée comme « valide » qu'à la fin du balayage lui-même.

Pour cette raison, les sorties du registre temporaire se connectent au registre de boucle du Matrix0 via les ports inter-matrice P13, P14 et P15.

Il est important d'observer sur la figure 16 que le registre temporaire est cadencé par la sortie DCMP OUT+ lorsque la comparaison des registres ADC-SPI aboutit à un nouveau max trouvé.

Le même signal OUT+ est transmis à Matrix0, SPI CLK Logic, via le port P10.

Étape 12: Configuration de l'appareil - Propriétés des composants Matrix1

Les Figures 17-19 montrent les fenêtres de propriétés des composants appartenant à Matrix1.

Étape 13: Résultats

Pour tester la mise en œuvre, un prototype de carte d'évaluation a été construit, où les 8 tensions d'entrée analogiques sont obtenues par une série de diviseurs de résistance avec TrimPots (comme illustré à la Figure 20).

Le multiplexeur utilisé est un ADG508, pièce pouvant fonctionner avec une seule alimentation (12 V).

Le pilote d'affichage à 7 segments est un 74LS47. Il décode un mot d'entrée parallèle et pilote directement un afficheur 7 segments à anode commune.

La carte d'évaluation dispose d'un connecteur à angle droit 2x10 à brancher directement sur une plate-forme de développement avancée GreenPAK au niveau de son connecteur d'extension, comme illustré à la Figure 21.

La conjonction avec la plate-forme de développement avancée GreenPAK rend très simple la prise de mesures des signaux pour un contrôle rapide. Par exemple, la Figure 22 montre un ensemble de signaux (respectivement CLOCK, sortie ADC INT et sortie DCMP OUT+) capturés par un analyseur logique HP 54620A. Les formes d'onde sont déclenchées par un front montant du signal OUT+ (sur l'oscilloscope étiqueté « A>B »), il s'agit donc d'une capture de forme d'onde lorsqu'une nouvelle tension maximale est détectée parmi les entrées analogiques. En fait, il a été obtenu en faisant tourner l'un des TrimPots de la carte d'évaluation pour augmenter la tension correspondante indiquée sur la figure 22.

La figure 23 montre le schéma de la Commission d'évaluation.

Conclusion

Dans ce Instructable, nous avons mis en œuvre un détecteur de tension max (ou min) à huit canaux à utiliser comme ajout commun aux systèmes de contrôle multicanaux. L'approche présentée exploite les fonctionnalités avancées des composants GreenPAK et montre comment il est possible d'intégrer dans une seule puce des fonctions analogiques et numériques. Plusieurs circuits intégrés commerciaux peuvent être remplacés par des Dialog GreenPAK afin de réduire la taille et le coût de l'application.

Conseillé:

Moniteur de tension pour batteries haute tension : 3 étapes (avec photos)

Moniteur de tension pour batteries haute tension : Dans ce guide, je vais vous expliquer comment j'ai construit mon moniteur de tension de batterie pour mon longboard électrique. Montez-le comme vous le souhaitez et connectez seulement deux fils à votre batterie (Gnd et Vcc). Ce guide suppose que la tension de votre batterie dépasse 30 volts, w

LIRE LA TENSION ANALOGIQUE - ARDUINO - RÉVÉLATION DE CODE #1 : 5 étapes

LIRE LA TENSION ANALOGIQUE - ARDUINO - CODE REVEAL #1: CODE REVEAL #1READ ANALOG VOLTAGE: Cet exemple vous montre comment lire une entrée analogique sur la broche analogique 0, convertir les valeurs de analogRead() en tension et l'imprimer sur la série moniteur du logiciel Arduino (IDE)

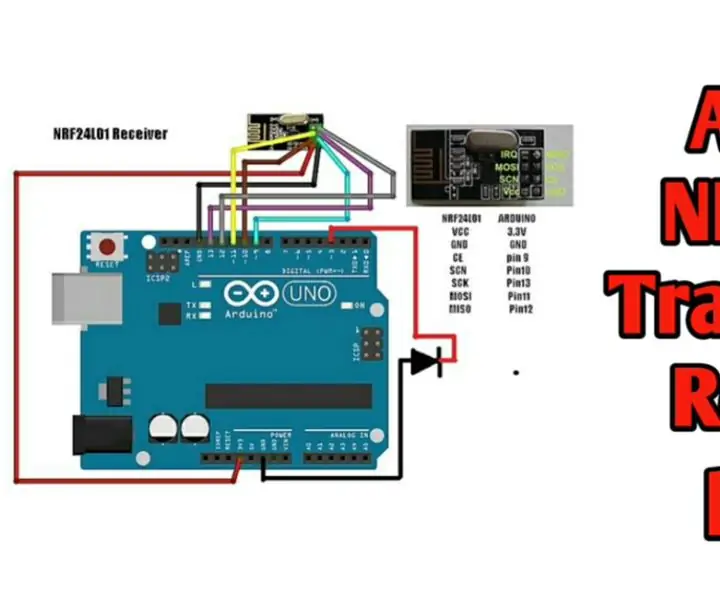

Télécommande sans fil utilisant le module 2.4Ghz NRF24L01 avec Arduino - Nrf24l01 4 canaux / 6 canaux émetteur-récepteur pour quadrirotor - Hélicoptère Rc - Avion Rc utilisant Ardu

Télécommande sans fil utilisant le module 2.4Ghz NRF24L01 avec Arduino | Nrf24l01 4 canaux / 6 canaux émetteur-récepteur pour quadrirotor | Hélicoptère Rc | Avion Rc utilisant Arduino: Pour faire fonctionner une voiture Rc | Quadricoptère | Drone | Avion radiocommandé | Bateau RC, nous avons toujours besoin d'un récepteur et d'un émetteur, supposons que pour RC QUADCOPTER nous ayons besoin d'un émetteur et d'un récepteur à 6 canaux et que ce type de TX et RX soit trop coûteux, nous allons donc en faire un sur notre

Amplificateur analogique 8 canaux pour PC ou HomeTheater : 12 étapes (avec photos)

Amplificateur analogique 8 canaux pour PC ou HomeTheater : c'est mon premier instructable. Je vais vous apprendre à fabriquer un amplificateur à 8 canaux pour un ordinateur ou un système audio avec des sorties analogiques séparées, je l'ai utilisé pour mon ordinateur de bureau, pour regarder des films, écouter de la musique HD et jouer à des jeux, en plus

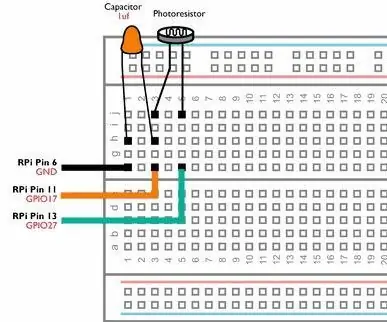

Circuits GPIO Raspberry Pi : Utilisation d'un capteur analogique LDR sans ADC (convertisseur analogique-numérique) : 4 étapes

Circuits GPIO Raspberry Pi : Utilisation d'un capteur analogique LDR sans ADC (convertisseur analogique-numérique) : Dans nos précédents Instructables, nous vous avons montré comment vous pouvez lier les broches GPIO de votre Raspberry Pi aux LED et aux commutateurs et comment les broches GPIO peuvent être hautes ou Faible. Mais que faire si vous souhaitez utiliser votre Raspberry Pi avec un capteur analogique ? Si nous voulons utiliser un