Table des matières:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:06.

- Dernière modifié 2025-01-23 14:45.

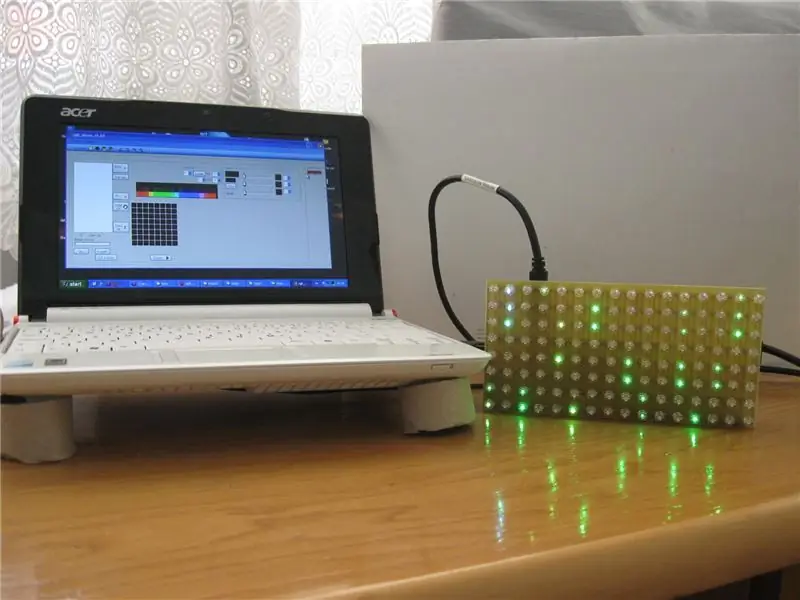

Dans ce projet, j'ai créé une matrice led 8x16 rgb en cascade et son contrôleur. Le 18F2550 de Microchip est utilisé pour son support USB. Les leds RVB sont pilotées par des registres à décalage 74hc595 avec des résistances. Pour les données d'animation et de configuration; L'eeprom externe 24C512 est utilisée. Les données de configuration et d'animation sont créées par l'interface utilisateur graphique (gui) sur l'ordinateur et transférées vers l'eeprom via USB. Et ils peuvent être attachés pour faire une plus grande zone d'affichage.

Étape 1: Architecture

architecture Les données d'animation et de configuration sont créées sur ordinateur par une interface graphique. puis il est téléchargé sur la carte de contrôle via USB. L'unité de microcontrôleur (mcu) transfère ces données à l'unité de stockage de la carte (eeprom). Lorsque la carte est en action, elle lit d'abord les données de configuration: intervalles de temps entre les images de l'animation, durée de l'animation à afficher, mode de fonctionnement (solo ou en cascade) puis elle lit une partie des données d'animation et envoie les données aux registres à décalage pour les mettre à jour l'état des leds. Des LED RVB anodiques communes sont utilisées. les leds sont disposées sur 8 lignes, 16 colonnes. toutes les anodes sont connectées les unes aux autres en rangée. Les registres à décalage contrôlent une ligne à la fois. Par multiplexage; 8 lignes sont mises à jour très rapidement afin que l'image continue soit affichée. pour 8 lignes --------- un registre à décalage de 8 bits est utilisé pour le multiplexage. pour 16 colonnes de leds rgb 16*3=48 ------ six registres à décalage de 8 bits sont utilisés. En mode solo, un module fonctionne comme décrit ci-dessus. En mode cascade: une carte devient une carte maître et envoie un signal de synchronisation aux autres cartes via une interface périphérique série (spi). toutes les cartes affichent des animations stockées dans leur mémoire. Et la synchronisation est arrangée selon le signal de synchronisation provenant de la carte maîtresse.

Conseillé:

MATRICE DE LED INTELLIGENT CONTRLÉE PAR INTERNET DIY (ADAFRUIT + ESP8266 + WS2812): 8 étapes (avec photos)

MATRICE DE LED INTELLIGENT CONTRLÉE PAR INTERNET DIY (ADAFRUIT + ESP8266 + WS2812): Voici ma 2ème avance vers un projet que je suis très heureux de vous montrer. Il s'agit d'une matrice de LED intelligente DIY qui vous permettra d'afficher des données, telles que YouTube Stats, vos Smart Home Stats, comme la température, l'humidité, peuvent être une simple horloge, ou simplement afficher

Matrice LED réactive audio DIY : 6 étapes

Matrice LED réactive audio DIY : Avez-vous déjà ressenti le besoin d'une matrice RVB cool avec fonction de réaction audio, mais avez-vous trouvé cela très difficile à fabriquer ou très coûteux à acheter ? Eh bien, maintenant votre attente est terminée. Vous pouvez avoir une matrice LED RVB Audio réactive dans votre pièce. Cet instru

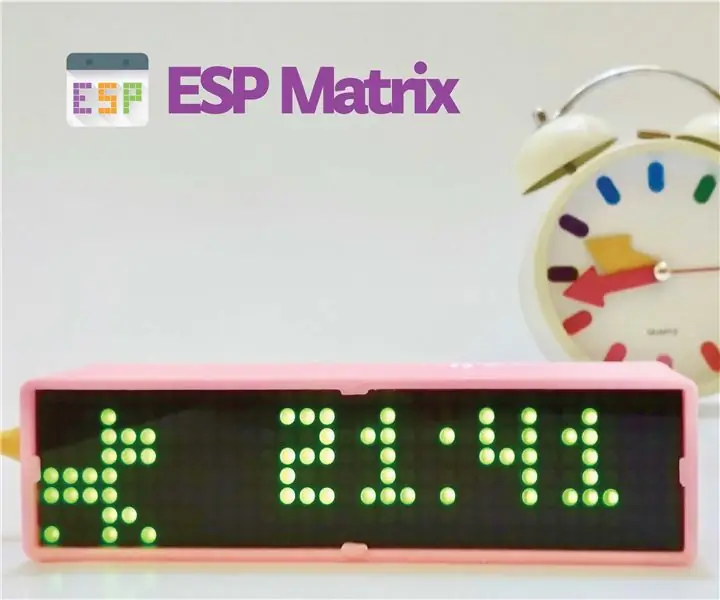

Utilisation de la matrice de points de l'horloge intelligente IoT Wemos ESP8266 - Matrice ESP : 12 étapes (avec images)

Matrice de points d'horloge intelligente IoT Utilisez Wemos ESP8266 - Matrice ESP: Créez votre propre horloge intelligente IoT qui peut: Afficher une horloge avec une belle icône d'animation Afficher Rappel-1 à Rappel-5 Afficher le calendrier Afficher les heures de prière musulmanes Afficher les informations météorologiques Afficher les informations Afficher les informations Afficher les conseils Taux Bitcoin Affichage

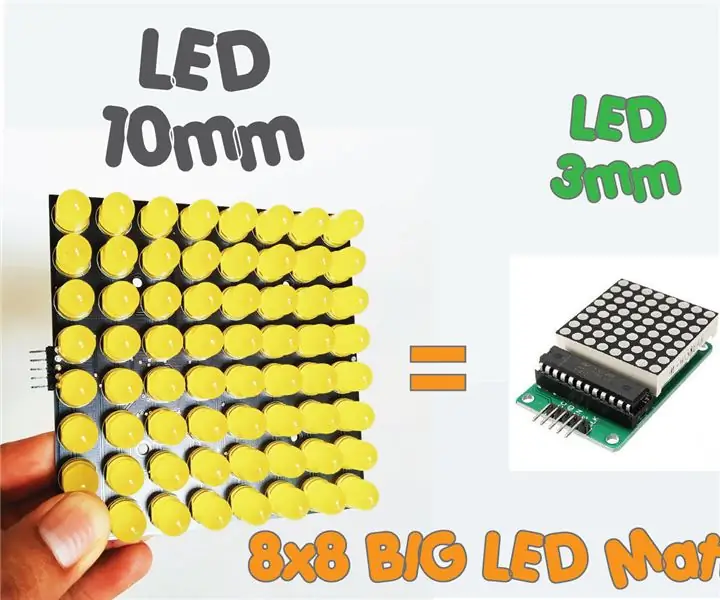

Comment construire une matrice LED 8x8 BIG (MAX7219 LED 10mm): 9 étapes (avec photos)

Comment construire une matrice LED 8x8 BIG (MAX7219 LED 10mm): Avez-vous travaillé avec une matrice LED 8x8 prête à l'emploi comme écrans? Ils existent en différentes tailles et sont assez intéressants à travailler. Une grande taille facilement disponible est d'environ 60 mm x 60 mm. Cependant, si vous recherchez une matrice LED prête à l'emploi beaucoup plus grande

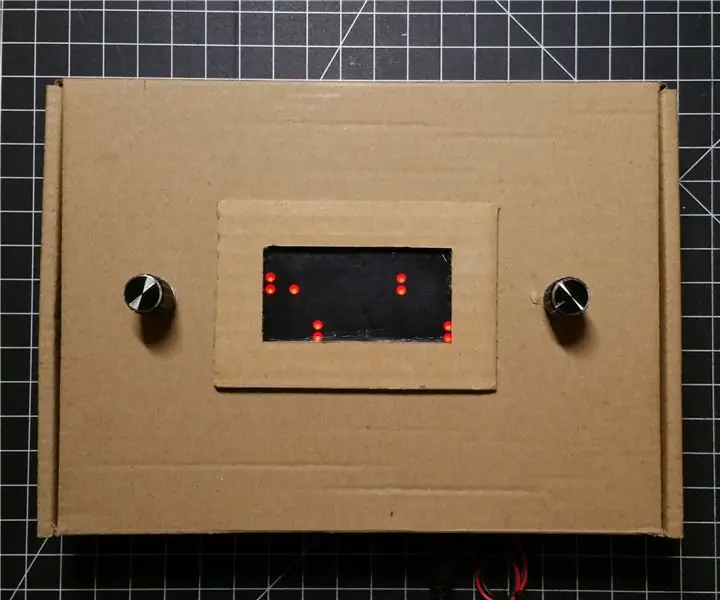

8x16 LED Matrix Pong Game (2 pagaies par version de joueur): 3 étapes

Jeu de Pong à matrice LED 8x16 (2 pagaies par version de joueur): J'ai été inspiré par de nombreuses variantes du jeu Pong classique implémenté sur Arduino en utilisant une matrice LED 8x8. Dans ce instructable, je vais vous montrer comment construire ma version préférée de Pong qui a deux pagaies - attaquant et gardien de but - par joueur