Table des matières:

- Étape 1: Ajoutez des sources et choisissez « Ajouter ou créer des sources de simulation

- Étape 2: Créez un fichier appelé Enable_sr_tb

- Étape 3: Créer un fichier de banc d'essai

- Étape 4: définissez Enable_sr_tb comme niveau supérieur sous la simulation

- Étape 5: Exécuter la synthèse et la simulation comportementale

- Étape 6: Évaluer le résultat de la simulation

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:09.

- Dernière modifié 2025-01-23 14:46.

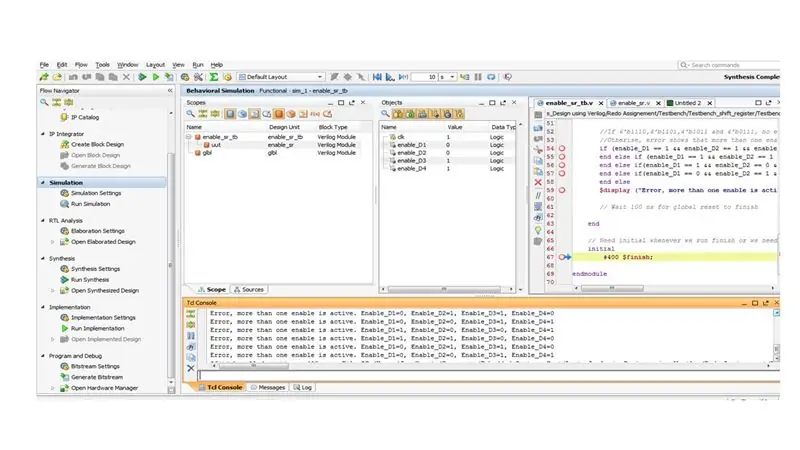

J'ai fait ce projet de simulation pour un cours en ligne. Le projet est écrit par Verilog. Nous utiliserons la simulation dans Vivado pour visualiser la forme d'onde dans enable_sr(enable digit) à partir du projet de chronomètre précédemment créé. De plus, nous utiliserons la tâche système pour afficher l'erreur que nous avons commise dans la conception.

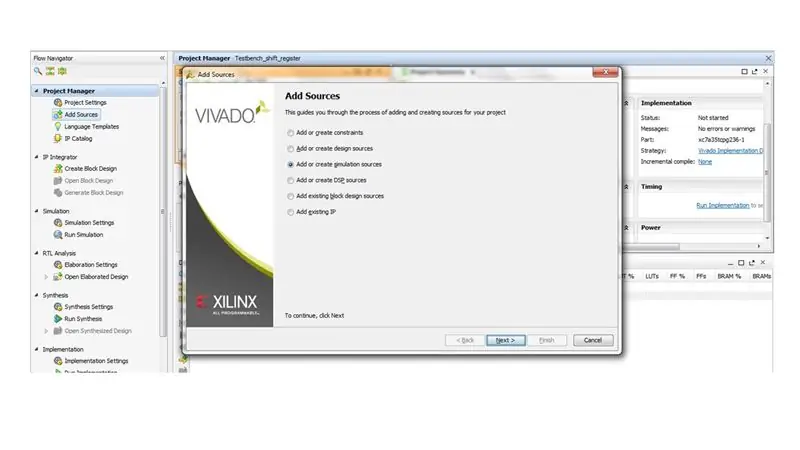

Étape 1: Ajoutez des sources et choisissez « Ajouter ou créer des sources de simulation

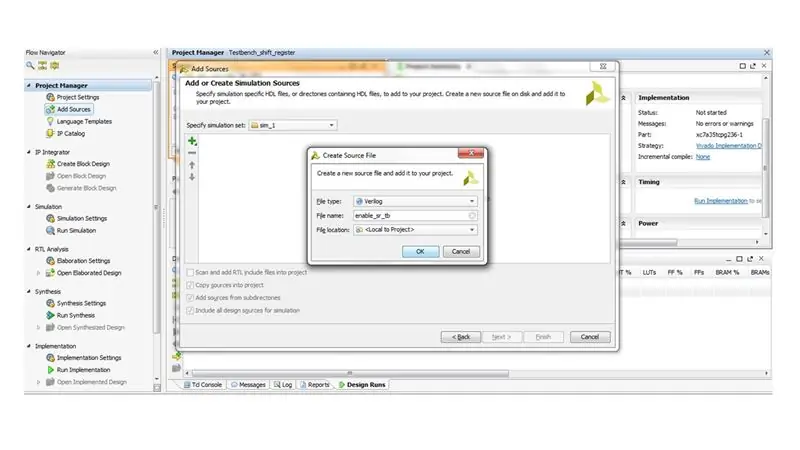

Étape 2: Créez un fichier appelé Enable_sr_tb

Étape 3: Créer un fichier de banc d'essai

1. Importez le module enable_sr du projet de chronomètre. C'est le fichier que nous voulons simuler

2. Créez le module de banc d'essai enable_sr_tb();

3. Saisissez les entrées et les sorties du module enable_sr(). N'oubliez pas que les entrées pour enable_sr sont maintenant de type registre tandis que les sorties deviennent de type net.

4. Instanciez l'unité sous test (uut) qui est le enable_sr

5. Générer une horloge dont la période (T) est de 20 ns

6. Utilisez l'instruction conditionnelle pour créer un système de vérification des erreurs. Dans cet exemple, nous voulons vérifier s'il y a plus d'un chiffre actif.

Remarque: Dans le fichier enable_sr() d'origine, nous devons initialiser le modèle en tant que 4'b0011 afin que deux chiffres soient actifs pour créer une erreur

7. Utilisez la tâche système $display pour afficher l'erreur

8. Utilisez la tâche système $finish pour terminer la simulation au temps 400ns

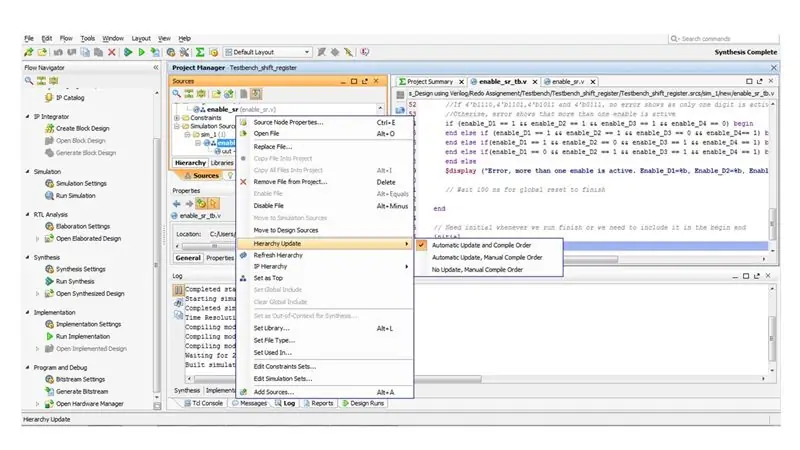

Étape 4: définissez Enable_sr_tb comme niveau supérieur sous la simulation

Étape 5: Exécuter la synthèse et la simulation comportementale

- Avant d'exécuter la simulation comportementale, exécutez la synthèse pour vous assurer qu'il n'y a pas d'erreurs de syntaxe dans le fichier testbench et l'unité sous test.

- Exécuter la simulation comportementale

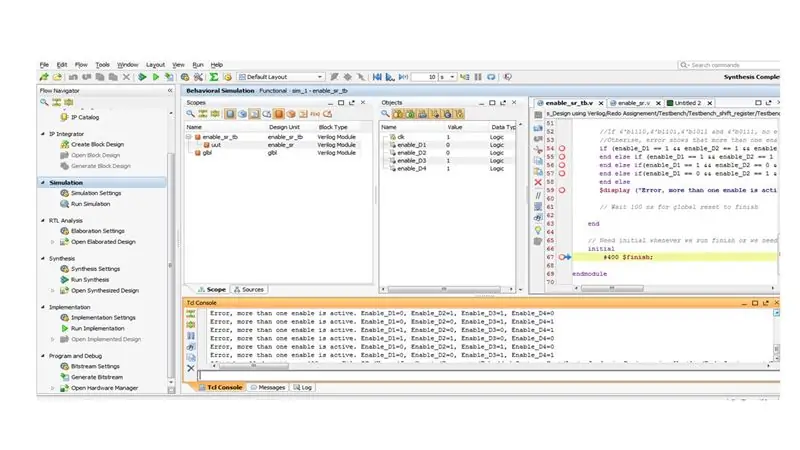

Étape 6: Évaluer le résultat de la simulation

Vous verrez les fenêtres de simulation. Il contient différents panneaux.

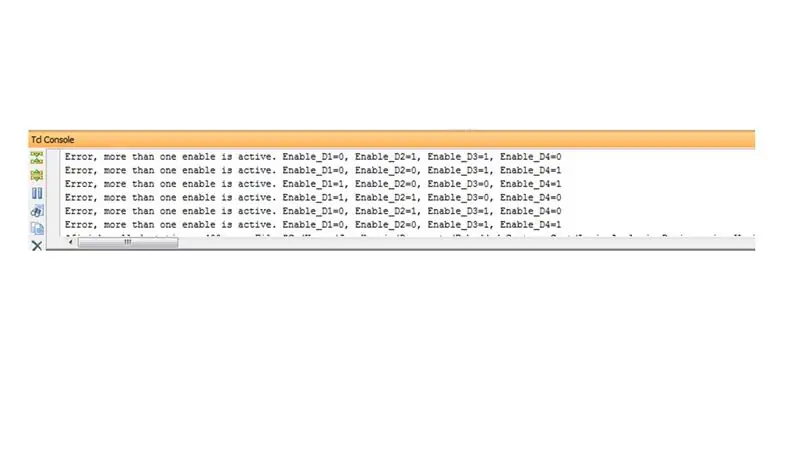

Vous verrez le message d'erreur dans le panneau de la console. Cela montre que plus d'un chiffre est actif pendant la période de simulation.

Vous pouvez également voir la forme d'onde dans la portée

Ci-joint le dossier du projet.

Conseillé:

Comment faire un enregistrement de la température et de l'intensité lumineuse - Simulation de Protée - Frittage - Liono Maker : 5 étapes

Comment faire un enregistrement de la température et de l'intensité lumineuse | Simulation de Protée | Frittage | Liono Maker : Salut, c'est Liono Maker, c'est ma chaîne YouTube officielle. Il s'agit d'une chaîne YouTube open source. Voici le lien : Liono Maker YouTube ChannelVoici le lien vidéo : Temp & Light Intensity LoggingDans ce tutoriel, nous allons apprendre à créer Temper

Comment créer un lecteur de démarrage Linux (et comment l'utiliser): 10 étapes

Comment créer un lecteur de démarrage Linux (et comment l'utiliser) : il s'agit d'une introduction simple sur la façon de démarrer avec Linux, en particulier Ubuntu

Comment utiliser le moteur pas à pas comme encodeur rotatif et écran OLED pour les étapes : 6 étapes

Comment utiliser le moteur pas à pas comme encodeur rotatif et écran OLED pour les étapes : Dans ce didacticiel, nous allons apprendre à suivre les pas du moteur pas à pas sur l'écran OLED. Regardez une vidéo de démonstration. Le crédit pour le didacticiel original va à l'utilisateur youtube "sky4fly"

Encodeur rotatif : comment ça marche et comment l'utiliser avec Arduino : 7 étapes

Encodeur rotatif : comment ça marche et comment l'utiliser avec Arduino : vous pouvez lire ceci et d'autres tutoriels incroyables sur le site officiel d'ElectroPeak. PrésentationDans ce tutoriel, vous apprendrez à utiliser l'encodeur rotatif. Tout d'abord, vous verrez des informations sur l'encodeur rotatif, puis vous apprendrez comment

Comment utiliser le terminal Mac et comment utiliser les fonctions clés : 4 étapes

Comment utiliser le terminal Mac et comment utiliser les fonctions clés : Nous allons vous montrer comment ouvrir le terminal MAC. Nous vous montrerons également quelques fonctionnalités du terminal, telles que ifconfig, le changement de répertoire, l'accès aux fichiers et arp. Ifconfig vous permettra de vérifier votre adresse IP, et votre annonce MAC