Table des matières:

- Auteur John Day day@howwhatproduce.com.

- Public 2024-01-30 09:06.

- Dernière modifié 2025-01-23 14:45.

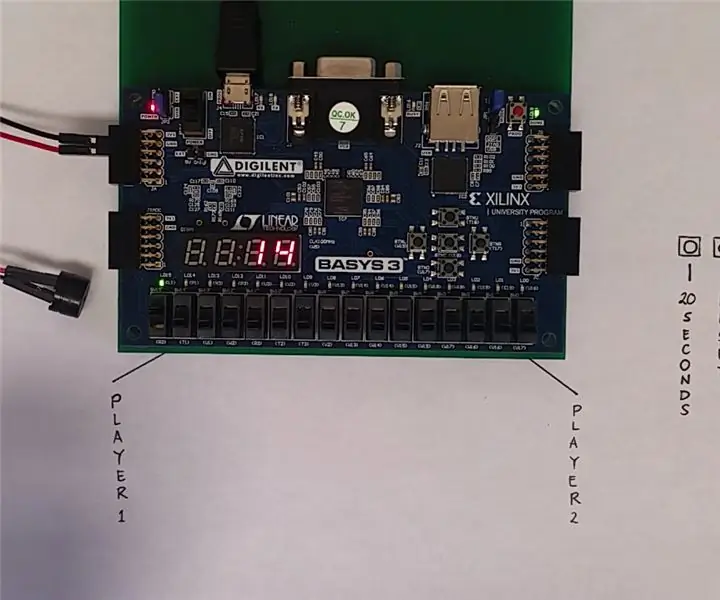

Le système de buzzer compétitif conçu dans ce projet fonctionne de la même manière que les systèmes de buzzer utilisés dans les compétitions régionales et nationales de Science Bowl. Ce projet a été inspiré par mon implication avec l'équipe du bol scientifique de mon lycée pendant trois ans. Nous avons toujours eu le désir de recréer le système de buzzer de verrouillage avec une minuterie de 5 secondes et 20 secondes.

Pour donner quelques informations sur le système de buzzer, les buzzers du bol scientifique sont programmés pour entrer un maximum de 8 joueurs (avec 8 buzzers séparés). Une fois qu'un buzzer a été pressé, le buzzer de la première personne s'allumera pour indiquer quel joueur reçoit la question. Le reste des joueurs sera "verrouillé", ce qui signifie que leurs buzzers ne répondront pas tant que le modérateur n'aura pas réinitialisé le système de buzzer.

Une fois que le modérateur aura lu les questions, il appuiera sur un bouton pour lancer le compte à rebours qui s'affichera sur l'affichage à sept segments. Après une question « tourner vers le haut », le modérateur peut appuyer sur le bouton droit pour lancer le compte à rebours à partir de 5 secondes. Pendant ce temps, après une question "bonus", le modérateur peut appuyer sur le bouton gauche pour lancer le décompte à partir de 20 secondes. Une fois que la minuterie atteint zéro, un avertisseur sonore indiquera que le joueur n'a plus de temps.

Pour réinitialiser le système et le compte à rebours, le modérateur peut appuyer sur le bouton central. Pour réinitialiser le mécanisme de verrouillage et les voyants du lecteur, les commutateurs du lecteur 1 et du lecteur 2 doivent être en position basse.

Étape 1: Matériaux

Vous aurez besoin des éléments suivants:

- Carte Basys3 (ou carte FPGA équivalente)

- Câble USB Micro-B

- Haut-parleur (j'ai utilisé un haut-parleur passif)

- 2 fils

- Logiciel à implémenter sur le FPGA (j'ai utilisé Vivado)

- Fichier du système de buzzer concurrentiel

Étape 2: Diagramme de la boîte noire

Le diagramme de la boîte noire montre les entrées et les sorties qui seront utilisées dans ce système de buzzer.

CONTRIBUTIONS:

player1, player2 Ces entrées sont connectées à deux commutateurs sur la carte Basys3. Pour plus de commodité, les commutateurs les plus à gauche et à droite seront utilisés.

reset Le bouton central sera utilisé pour représenter le bouton reset.

count_down_20_sec Le bouton gauche sera utilisé pour représenter le bouton de la minuterie de 20 secondes.

count_down_5_sec Le bouton droit sera utilisé pour représenter le bouton de la minuterie de 20 secondes. Pour vous assurer que les minuteries de 20 secondes et de 5 secondes démarrent, maintenez le bouton enfoncé jusqu'à ce que l'affichage à sept segments affiche la minuterie.

CLK La carte FPGA générera une horloge qui fonctionnera avec une fréquence de 10 ns.

LES SORTIES:

haut-parleur La sortie haut-parleur est connectée à un buzzer ou un haut-parleur externe. Vous devrez connecter l'enceinte aux ports JA pmod de la carte Basys3. Cette étape sera décrite ci-dessous.

speaker_LED Cette sortie est connectée à une LED au centre de la carte et indiquera simplement quand la sortie du haut-parleur du FPGA est élevée. Vous pouvez l'utiliser pour tester votre haut-parleur externe. Notez que certains des ports pmod peuvent ne pas fonctionner correctement, vous pouvez donc en essayer différents et utiliser la LED pour vérifier si le haut-parleur doit être allumé.

SEGMENTS Cette sortie est connectée aux huit segments individuels de l'affichage à sept segments, y compris le point décimal.

DISP_EN Cette sortie est connectée aux quatre anodes de l'afficheur à sept segments.

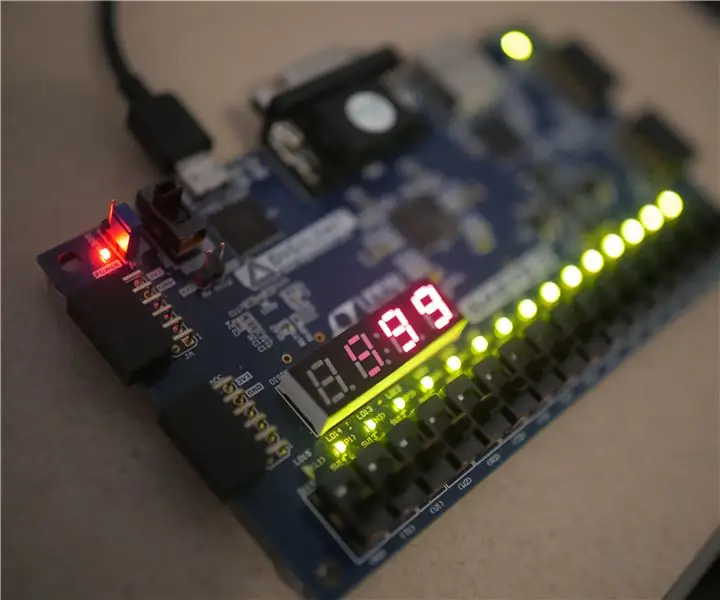

player_LED Cette sortie est un signal à 2 faisceaux qui est connecté aux LED au-dessus des commutateurs player1 et player2. Le premier joueur à basculer son interrupteur correspondant sera indiqué par la LED. Notez que les deux LED ne peuvent pas être allumées simultanément.

Étape 3: connexion du haut-parleur externe

Pour connecter le haut-parleur externe à la carte Basys3, prenez vos deux fils et attachez-les comme indiqué sur l'image ci-dessus. La ligne blanche relie la borne négative du haut-parleur au port de masse de la carte. La ligne rouge relie la borne positive du haut-parleur au port JA10 pmod de la carte.

Le fichier de contraintes est conçu pour que tout port de JA1 à JA10 fonctionne. Cependant, certaines broches de la carte ne répondent pas, donc si JA10 ne fonctionne pas, vous pouvez essayer les autres ports.

Étape 4: Diagramme structurel

L'image ci-dessus montre le schéma structurel du système de buzzer concurrent, y compris tous les composants qui composent le module principal. Leurs descriptions sont les suivantes:

player_lockout_LED1 Le composant LED de verrouillage du lecteur est une machine à états finis qui utilise un codage one-hot. Il a quatre entrées: player1, player2, reset et CLK. Il contient une sortie de bundle 2 bits player_LED. Les entrées et sorties du composant player_lockout_LED1 sont toutes directement connectées aux entrées et sorties de même nom du module principal.

buzzer_tone1 Le composant buzzer est basé sur ce code posté sur un forum

stackoverflow.com/questions/22767256/vhdl-… Cependant, il a été modifié pour produire un son continu avec une fréquence de 440 Hz (une note). L'entrée d'activation est connectée à un signal buzzer_enable qui est une sortie du composant down_counter_FSM1.

clk_div1 Le composant de diviseur d'horloge est une version modifiée du diviseur d'horloge du professeur Bryan Mealy fourni sur PolyLearn. Il ralentit l'horloge de sorte que la période de sortie est de 1 seconde.

down_counter_FSM1 Le décompteur est un FSM conçu pour décompter jusqu'à zéro. Les deux heures de démarrage possibles sont 20 ou 5 qui sont choisies par l'utilisateur. Il affiche « 1 » lorsque la minuterie a atteint zéro pour indiquer que le temps est écoulé. Cette sortie agit comme une validation pour le composant de tonalité de buzzer. Le compteur émet également un signal de faisceau de 8 bits qui envoie un BCD de 8 bits qui est envoyé au décodeur de segment. Une autre sortie est le counter_on qui est également connecté à l'entrée valide du décodeur de segment.

sseg_dec1 Le composant décodeur à sept segments est fourni sur PolyLearn et a été écrit par le professeur Bryan Mealy. Il utilise une entrée BCD fournie par le down_counter_FSM1 et affiche l'équivalent décimal sur l'affichage à sept segments. Lorsque le compteur est activé, l'entrée valide est élevée. Cela permet au décodeur d'afficher le nombre décimal sur l'affichage à sept segments. Lorsque le compteur est éteint, l'entrée valide est faible. L'affichage à sept segments n'affichera alors que quatre tirets.

Étape 5: Diagramme de la machine à états finis (FSM)

La liste de sensibilité pour la machine à états finis comprend player1, player2, reset et l'horloge. La sortie FSM est un bundle player_LED de 2 bits connecté à deux LED sur la carte Basys3. La machine à états finis affiche les trois états suivants:

ST0 est l'état de départ. Dans cet état, les deux LED sont éteintes. Le FSM restera dans cet état si player1 et player2 sont tous les deux bas. Une réinitialisation asynchrone définit également l'état sur ST0. Lorsque le commutateur player1 est réglé sur high, l'état suivant sera ST1. Si le commutateur player2 est réglé sur high, l'état suivant sera ST2.

ST1 est l'état pour lequel la LED player1 est allumée. Le FSM restera dans cet état pour toute entrée. Cela signifie que même lorsque le commutateur player2 est réglé sur haut immédiatement après que le commutateur player1 soit haut, il restera dans ST1. Seule la réinitialisation asynchrone peut définir l'état suivant sur ST0.

ST2 est l'état pour lequel la LED player2 est allumée. Semblable à ST!, le FSM restera dans cet état pour n'importe quelle entrée, même lorsque le commutateur player1 est réglé sur high immédiatement après que le commutateur player2 soit sur high. Encore une fois, seule la réinitialisation asynchrone peut définir l'état suivant sur ST0.

Conseillé:

Système d'alerte de stationnement en marche arrière Arduino - Étapes par étape : 4 étapes

Système d'alerte de stationnement en marche arrière Arduino | Étapes par étape : dans ce projet, je vais concevoir un circuit de capteur de stationnement inversé pour voiture Arduino simple à l'aide d'un capteur à ultrasons Arduino UNO et HC-SR04. Ce système d'alerte de marche arrière basé sur Arduino peut être utilisé pour une navigation autonome, une télémétrie de robot et d'autres r

Système de tri des couleurs : système basé sur Arduino avec deux courroies : 8 étapes

Système de tri par couleur : Système basé sur Arduino avec deux courroies : Le transport et/ou l'emballage des produits et articles dans le domaine industriel se fait à l'aide de lignes réalisées à l'aide de courroies transporteuses. Ces courroies aident à déplacer l'article d'un point à un autre avec une vitesse spécifique. Certaines tâches de traitement ou d'identification peuvent être

Système d'alarme incendie utilisant Arduino [en quelques étapes faciles] : 3 étapes

![Système d'alarme incendie utilisant Arduino [en quelques étapes faciles] : 3 étapes Système d'alarme incendie utilisant Arduino [en quelques étapes faciles] : 3 étapes](https://i.howwhatproduce.com/images/003/image-6841-j.webp)

Système d'alarme incendie utilisant Arduino [en quelques étapes faciles] : Vous cherchez à faire un projet simple et intéressant avec Arduino qui en même temps pourrait être vraiment utile et potentiellement sauver des vies ? Si oui, vous êtes au bon endroit pour apprendre quelque chose de nouveau et d'innovant. Dans cet article, nous allons

Jeu de chronométrage VS compétitif à 2 joueurs : 4 étapes

Jeu de chronométrage VS compétitif à 2 joueurs : vous aurez besoin de : 1.Digilent Basys 3, carte FPGA (ou tout autre FPGA)2. Une version relativement à jour de Vivado, ou un autre environnement VHDL3. Un ordinateur qui peut exécuter le programme mentionné

Comment connecter et configurer correctement un mini système d'étagère HiFi (système audio) : 8 étapes (avec photos)

Comment connecter et configurer correctement un mini système d'étagère HiFi (système audio) : je suis une personne qui aime apprendre l'ingénierie électrique. Je suis une école secondaire à l'école Ann Richards pour les jeunes femmes leaders. Je fais cette instructable pour aider tous ceux qui veulent profiter de leur musique à partir d'un Mini LG HiFi Shelf Syste